第7回 JTAGテストとHALTを活用した品質保証の取り組み

2021年03月23日

「HALT」をご存知ですか?

HALTは、1980年代に米国で発案され、欧米を中心に航空機、自動車、電気製品部品の信頼性評価に採用されているテスト手法です。高加速度限界テスト「Highly Accelerated Limit Test」の略語でHALT(ホルト)と呼ばれています。製品化プロセスの初期段階の開発と設計において、短期間で製品の弱点を検出するための試験システムのことです。HALTは、近年欧米企業のみならずアジアにも拡大し、今後日本でも拡大していくことが予測されている注目の品質保証の方法です。HALT試験装置は、図1のように用途に合わせて、さまざまな製品が用意されています(なお、図中にあるHASSについては後述します)。

HALTは、製品の信頼性予測(寿命予測)を行うものではなく、製品仕様を超える「強いストレス」を製品に与え、製品の稼働限界と破壊限界を見つけるものです。「強いストレス」とは急速温度変化による温度ストレスと6自由度振動による振動ストレスであり、それらのストレス試験を組み合わせた5つのステップ(①低温ステップ試験、②高温ステップ試験、③温度急変サイクル試験、④振動ステップ試験、⑤温度急変と振動の複合試験)で構成されています。製品の弱点を短期間で検出し、改善改良を繰り返すことで製品の信頼性を向上させることができます。

今回は、JTAGテストとHALTを組み合わせた品質保証の取り組みと実例をご紹介します。

BGAはんだ接合部の信頼性評価方法の課題

電子機器の小型化と高性能化に伴い、BGAパッケージ部品の小型化が進んでいます。製品基板の検査では、不良品の市場流出を防ぐことと製品寿命を担保するための品質保証が重要です。BGA部品においては、はんだ接合部の信頼性評価試験により、製品の品質保証が行われています。

従来は、デイジーチェーン接続と呼ばれる配線設計された評価専用のBGA部品をメーカーから入手して、製品基板とは別に評価専用の基板を用意する必要がありました。また、はんだ接合部をピンポイントで観察することができないため、はんだ不良の箇所を特定するためには、断面観察などが必要となり時間とコストがかかることが課題となっていました。

しかし、JTAGテスト(バウンダリスキャン)であれば、製品基板を使ってBGA部品の実装テストを行うことができるため、HALTとJTAGテストを組み合わせることにより、信頼性評価を製品基板で行うことができるようになりました。

HALT試験装置とJTAGテストの結合テスト

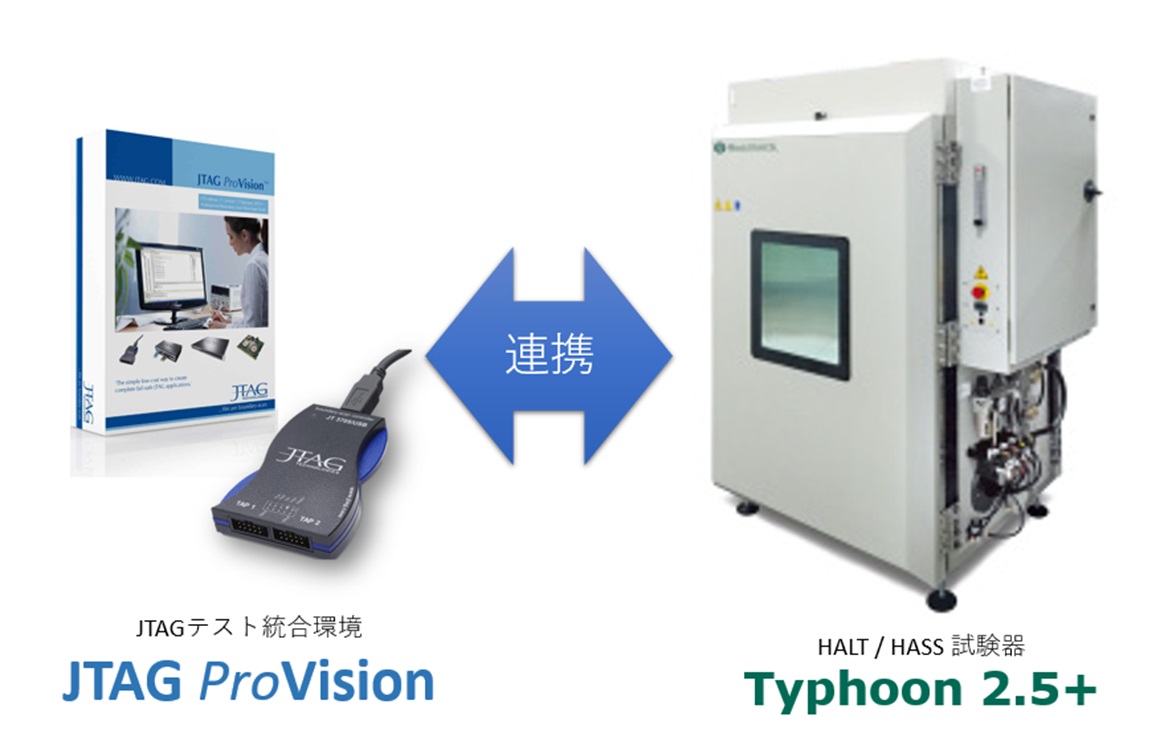

JTAGテストシステム「JTAG ProVision」と結合したHALT試験装置「Typhoonシリーズ」は、エスペック株式会社のHALT試験装置の代表的な製品で、製品開発プロセスの初期段階でHALTを実施することで、製品の信頼性を高めることができます。

またHASS(Highly Accelerated Stress Screen)にも対応しており、HALTで得られた限界試験データを基に、量産品の製造工程での変化やばらつき、潜在的不具合がないかを監視するためのスクリーニングをすることができます。お客様の製品サイズや数量、重量に合わせた試験機があり、テーブルサイズは457×457mm~2540×1219mm、テーブル最大積載重量は36~544kgまで対応しています。最大加速度75Grmsの6自由度振動と-100℃~250℃の広温度範囲、70~100℃/minの急速な温度変化を実現できます。また、効率的な気流特性とテーブル位置を変更できる構造で、液体窒素や電力コストを削減することができます。

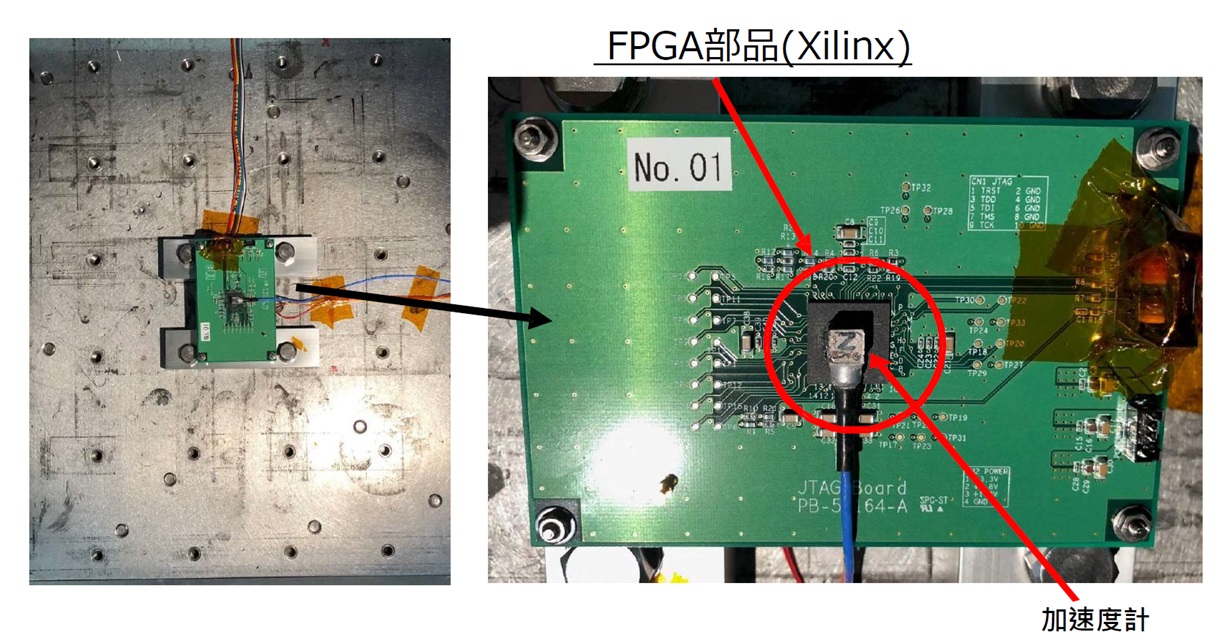

今回は、FPGA(BGAパッケージ、196ピン)を搭載した基板で信頼性評価を行いました。HALT試験装置へは、図3のようにアルミフレームに4隅で固定しました。HALTでは、基本的に治具設計基準として加速度については、テーブル制御加速度≦試料加速度となるように設定をします。短時間で信頼性評価を行うために、HALT試験装置の加速度を70 [Grms]に設定し、FPGA付近の加速度を120 [Grms]として試験を行うことにしました。

試験条件は、温度条件を設定せずに常温とし、HALT振動試験の合計時間は100分、HALT試験装置の加速度を70 [Grms]と設定し、5分間実行と1~2分間停止を20回繰り返しました。JTAGテストのサンプリング時間は30秒として、HALT振動試験を行っています。100分間連続実行して、FPGAのピンをバーチャルプローブとしてBGA部品のはんだ接合状態をスキャンしました。

HALT試験の結果 (スタティック状態)

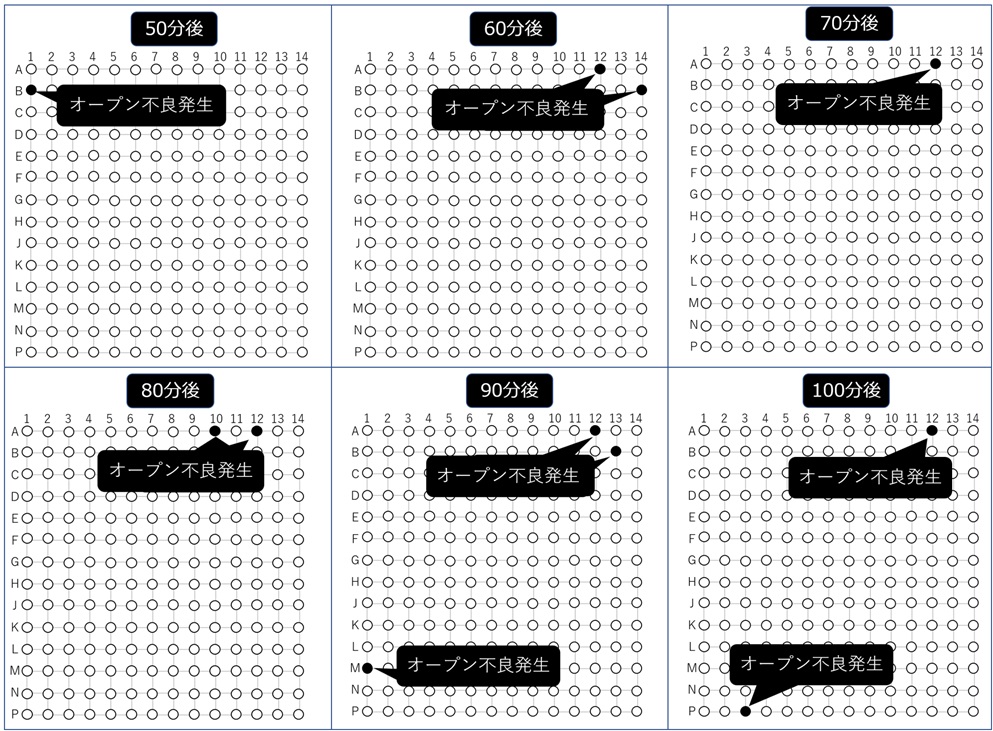

HALT振動試験を、5分間実行と1~2分間停止を繰り返して行い、振動を停止した状態(スタティック状態)でJTAGテストを行った結果は図4のようになりました。図中の白丸は、BGAのピン配列を示していて、A1ピンからP14ピンまでの196ピンのBGAパッケージのはんだ信頼性試験を行った結果です。今回は、50分経過後から10分間隔の試験結果を紹介します。開始から50分経過したところで、左上のB1ピンでオープン不良が検出され、60分を経過したあたりから右上のA12ピン、B14ピンのオープン不良が現れました。90分が経過すると、左下のM1ピンとP3ピンにオープン不良が現れるようになりました。BGA部品に振動を与えて、振動を止めた状態でJTAGテストにより電気試験を行っています。そのため、振動が止まったタイミングでBGAのボールと基板のパッドが浮いたときに不良が検出され、はんだが剥離してもボールと基板が接触しているときには、不良が検出されていないことがわかります。

HALT試験の結果 (ダイナミック状態)

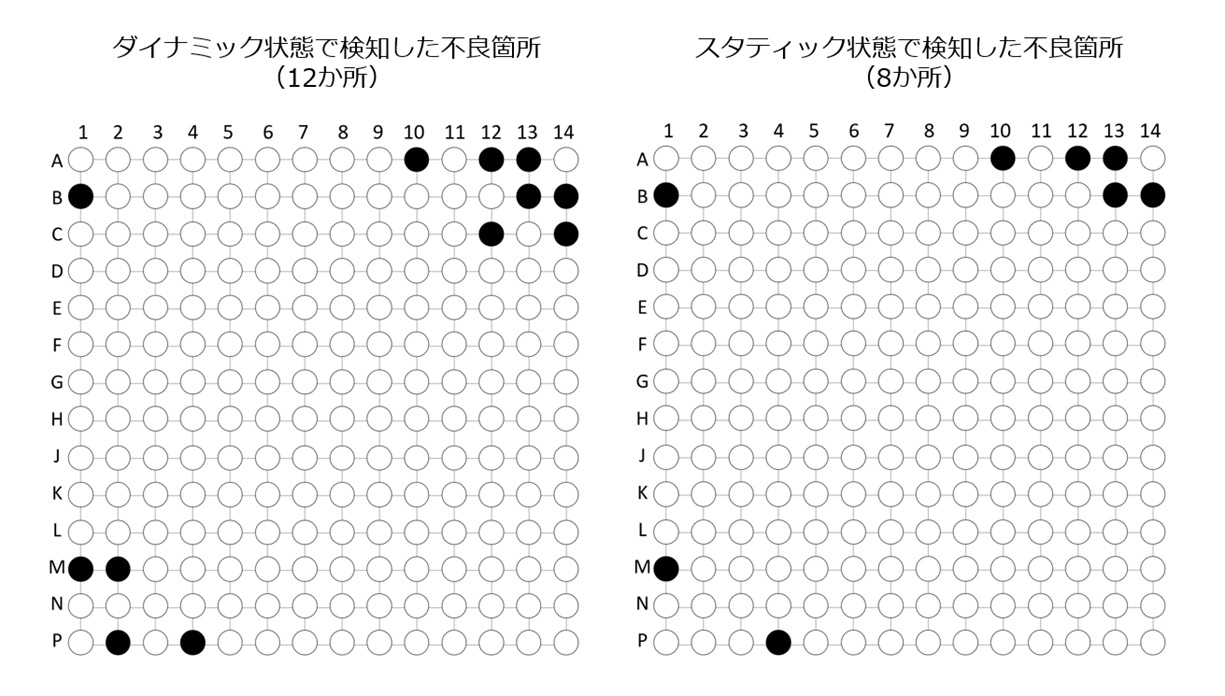

次に同様に、HALT振動試験を、5分間実行と1~2分間停止を繰り返して行い、ダイナミック状態(振動中)のJTAGテストでBGAはんだ状態を測定しました。スタティック状態とダイナミック状態を比較すると、図5のようにHALT振動試験の結果に差異を確認しました。図中の黒丸の箇所は、試験全体の中で各状態において、1回以上オープン不良を検知した箇所です。ダイナミック状態で検出したオープン不良が12か所に対して、スタティック状態で検出したオープン不良は8か所となりました。この結果から、ダイナミック状態でテストを行うと、振動の影響で瞬間的にオープンした場合でも不良箇所として特定できるため、検出精度が高くなることがわかります。

短時間で製品の弱点を見つけられるHALT試験

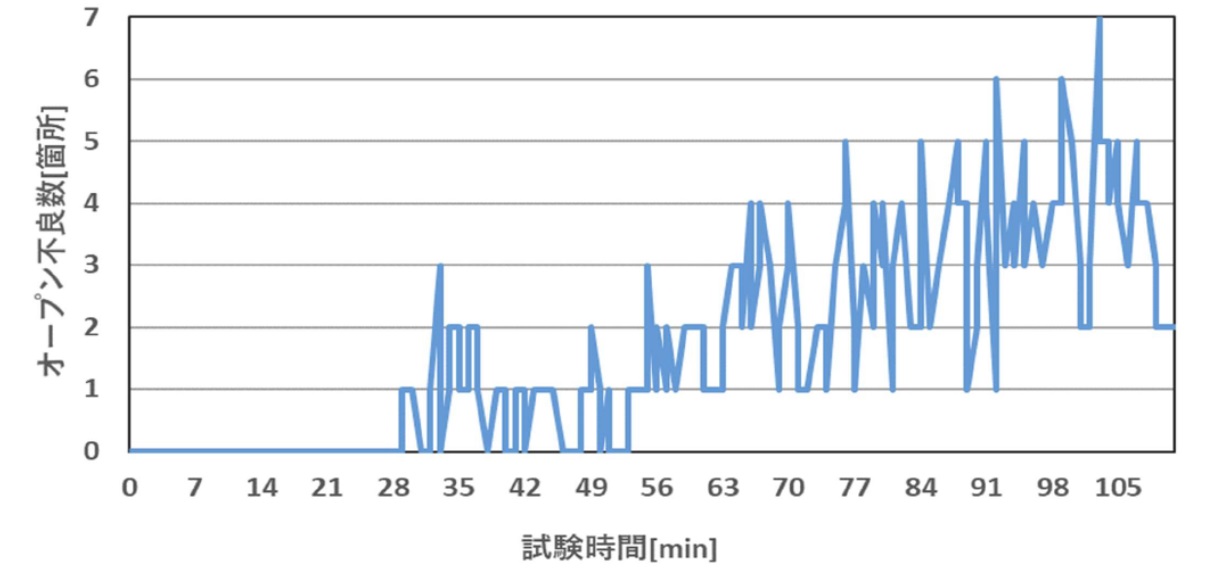

ダイナミック状態とスタティック状態を含めたHALT振動試験全体での、時間経過に伴う不良検出数を図6.に示します。HALT振動による影響で時間が経過すると、BGAのボールの状態が正常から半断線、断線へと変わっていきます。振動とサンプリングしたタイミングにより、BGAのボールと基板が接触しているか、接触していないかにより、合否判定が変わるため、オープン不良箇所の検出数が上下に振れています。しかし、時間が経過するにつれ、オープン不良が増えていることがわかりました。

HALT試験装置とJTAGテストを組み合わせた大きなメリットは、製品基板のBGAパッケージを試験対象にできることです。また、試験時間が2時間未満と、非常に短時間で信頼性を評価することができます。HALT試験が終わると、故障箇所を特定できているため、断面解析箇所を最小限に抑えられ、分析コストの削減と分析期間の短縮もメリットとなります。分析結果は、プリント基板のレイアウト設計、はんだ材料、はんだの温度プロファイルなどにフィードバックすることができ、製品の信頼性向上と製品寿命の延長が可能となります。

読者の皆さまの現場でも、製品の品質保証の取り組みとして、ぜひ導入をご検討いただければと思います。

次回予告「実装基板の最新動向と検査の課題を解決するハイブリッド検査」

2021年2月4日に、エレクトロニクス実装学会(JIEP)の「検査&ものづくりイノベーション研究会」の公開研究会が行われました。その中で「実装基板の課題を解決するハイブリッド検査とテスト容易化設計DFTの重要性」について講演しました。

次回は、その講演内容から「実装基板の最新動向と検査の課題を解決するハイブリッド検査」というテーマで、皆さまの製品基板の動向と検査の課題、また課題を解決するためのハイブリッド検査とテスト容易化設計についてご紹介します。

第1回 試作基板のBGA部品が動かない!?第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |