第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

2020年08月20日

その基板、テストパッドを半分にできますか?

製品の高性能化と小型化が進み、基板のレイアウト設計にあたっては部品の配置とパターンの配線だけでも相当な苦労をされているのではないでしょうか。それに加えて、デバッグや量産テストのためのテストパッドを数多く配置するのは至難の業です。

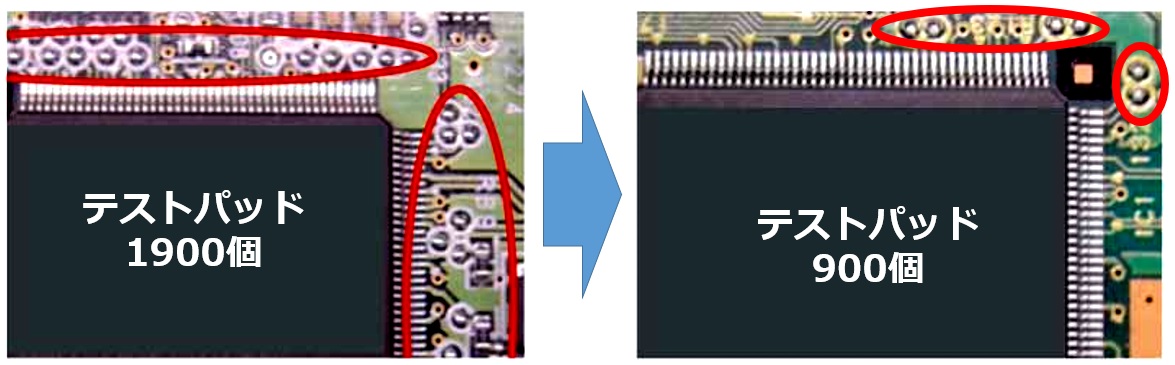

図1は、JTAGテストのDFTサイクルを実践して、テストパッドを53%削減したお客様の事例です。QFP(Quad Flat Package) 部品の周辺にテストパッドが配置されていますが、大幅に削減できていることが分かります。JTAGテストはBGAパッケージのテストに有効ですが、QFPを用いた基板でもテストパッドの削減に効果があります。

今回は、テストパッドの削減とデバッグに役立つJTAGテストツールをご紹介します。

テストパッドを減らすためにテストカバレッジを検証する

「テストパッドを削減したい!」という課題をお持ちのお客様は非常に多く、「設計段階では基板のレイアウト設計の負担を減らしたい」「品質保証ではノイズ源となってしまう」という話を伺います。

実は量産段階においてもテストパッドを減らしたいという声は多く、検査装置のプローブピンをテストパッドに接触させて検査するのですが、プローブピンが増えるほど接触不良による誤診断(虚報)が発生してしまい、テストをリトライする回数が増えてしまいます。そのため、テスト時間が延び、結果として検査コストも増えてしまい、企業の利益が減ってしまうという課題もあります。

テストパッドを削減するためには、導通テスト向けに配置したテストパッドをJTAGテストのバーチャルプローブに置き換えることが効果的です。したがって、これまで紹介してきたJTAGテスト容易化設計(DFT)とDFTサイクルにより、回路設計段階でJTAGテストカバレッジを最大化することが重要になります。

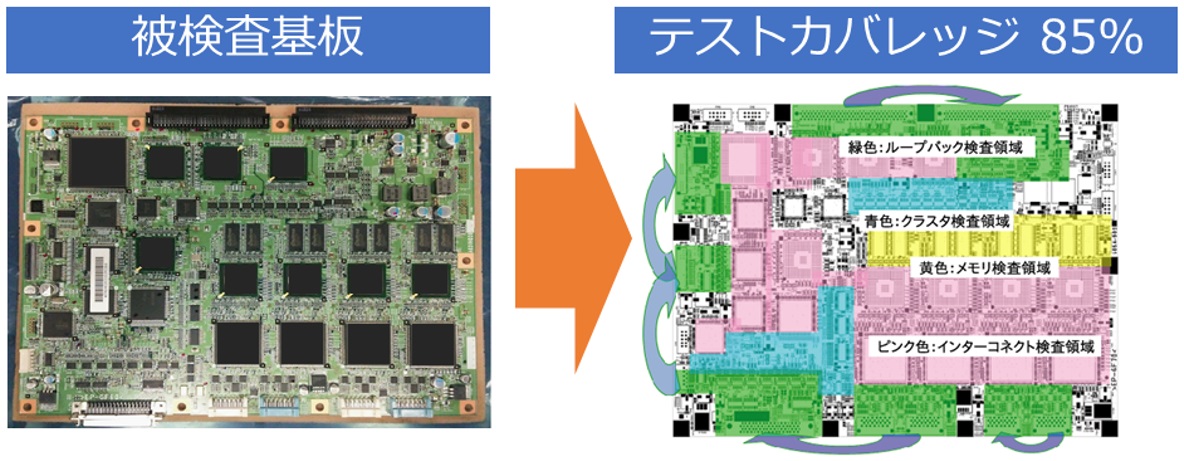

図2は実際にDFTサイクルを実践され、テストカバレッジを85%まで拡大したお客様の事例です。色が塗られている範囲は、JTAGテストで検査できる範囲を示しています。逆に色が塗られていない範囲は、テストパッドを配置してプローブピンを使って量産時の出荷テストを行っています。

JTAGテストツールは簡単に繋がります

JTAGテストは、図3のように検査対象の基板をJTAGコントローラから制御して、実装されている部品(マイコン、FPGAなど)の端子をバーチャルプローブとしてテストできる仕組みです。また、コネクタの実装テストを行うためのIOモジュールも用意されています。

JTAGコントローラを接続するためには、試作基板のFPGAダウンロード用のJTAGコネクタ、マイコンのソフトウェア開発用のJTAG ICE用のデバッグポートを使うことができ、簡単に接続することができます。量産のときには、コネクタは実装されないケースが多いため、量産用の検査治具からプローブピンで基板上のJTAGの信号に接触してテストします。

開発効率を改善するには試作基板の受入検査が重要です

試作基板が完成すると電源とGNDがショートしていないかチェックして、マイコンのプログラムやFPGAのロジックをダウンロードしてデバッグを始めているのではないでしょうか?

連載の第3回でご紹介した「試作BGA基板の不具合発生例」のように、モノづくりに問題がある基板でデバッグを始めてしまうと、無駄な作業が増えてしまいプロジェクトが遅延してしまいます。

JTAGテストでは、試作基板の回路図情報からテストアプリケーションが自動生成されるため、試作基板が完成するときには受入検査のテスト準備が整っていることになります。試作基板のデバッグを始める前に、JTAGテストを活用して受入検査を行うと、モノづくりの不具合の有無をデバッグ前に確認することができます。したがって、製造不良による無駄なデバッグ作業を削減して、開発効率を改善することができます。

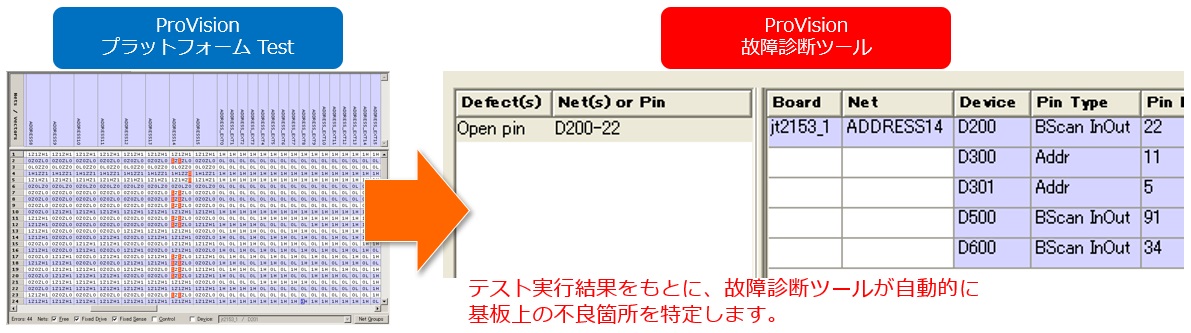

もし、不具合があった場合には、図4のようにモノづくり上の不良箇所が自動的に診断され、はんだのオープン不良、ブリッジ不良、基板のパターン不良などの場所を短時間で特定することができます。修理した基板は、再度JTAGテストを実行して不具合がなくなったことを確認できます。

FPGAから任意の波形を簡単に出力できます

FPGA基板をデバッグするときに、FPGAから周辺回路に対して、任意の波形を出力するのは大変ですよね? 特に大規模なFPGAをお使いの方は、周辺回路のテストのためにロジックを設計して、コンパイル、シミュレーション、ダウンロードするのは大変な労力と時間がかかっていると思います。

また、マイコンの場合には、ソフトウェアを設計して、コンパイル、書き込みという手順が必要となり、やはり大変な労力がかかります。回路設計者からソフトウェア設計者にデバッグ用のソフトウェア開発の依頼をして、その完成を待つ時間もかかってしまうのではないでしょうか。

しかし、JTAGテストを使うと、部品の端子に内蔵されたバーチャルプローブから、任意の波形を簡単に出力することができるのです。したがって、回路設計者が単独で周辺回路をデバッグすることができるようになります。FPGAの内部ロジックを使うわけではありませんし、マイコンのソフトウェアを使うわけでもありませんので、コンパイルする時間も、書き込む時間もかかりません。

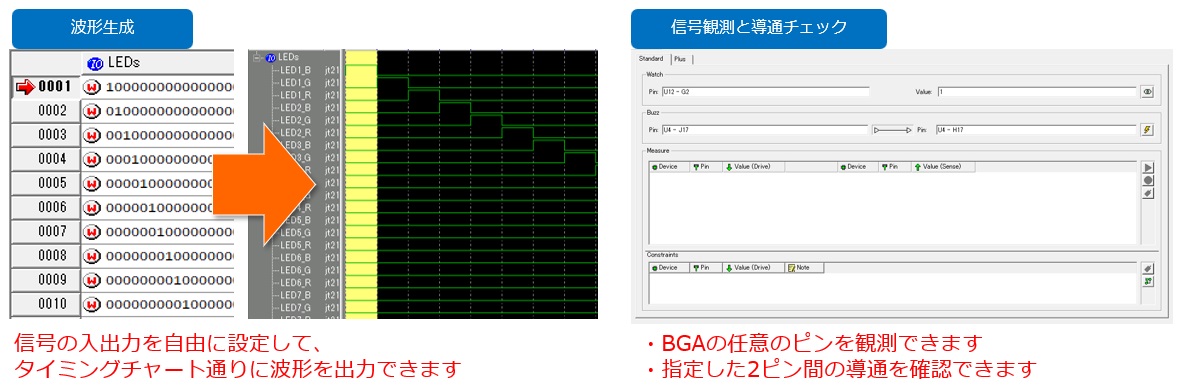

図5のように、任意の指定したピンから自由にHighレベル(1)、Lowレベル(0)の設定を行うことにより、任意の波形を出力することができます。また、入力信号の期待値を設定すると、期待値通りの信号が入力されたかモニタすることもできます。

また、テスターではプロービングできないBGA基板のデバッグに役立つ、信号観測ツールと導通チェックツールも用意されています。BGA部品とBGA部品とが内層で配線されていると、本当に導通しているか確認するのは大変ですが、このツールがあれば安心です。

試作基板のデバッグから量産テストまで使える豊富な機能

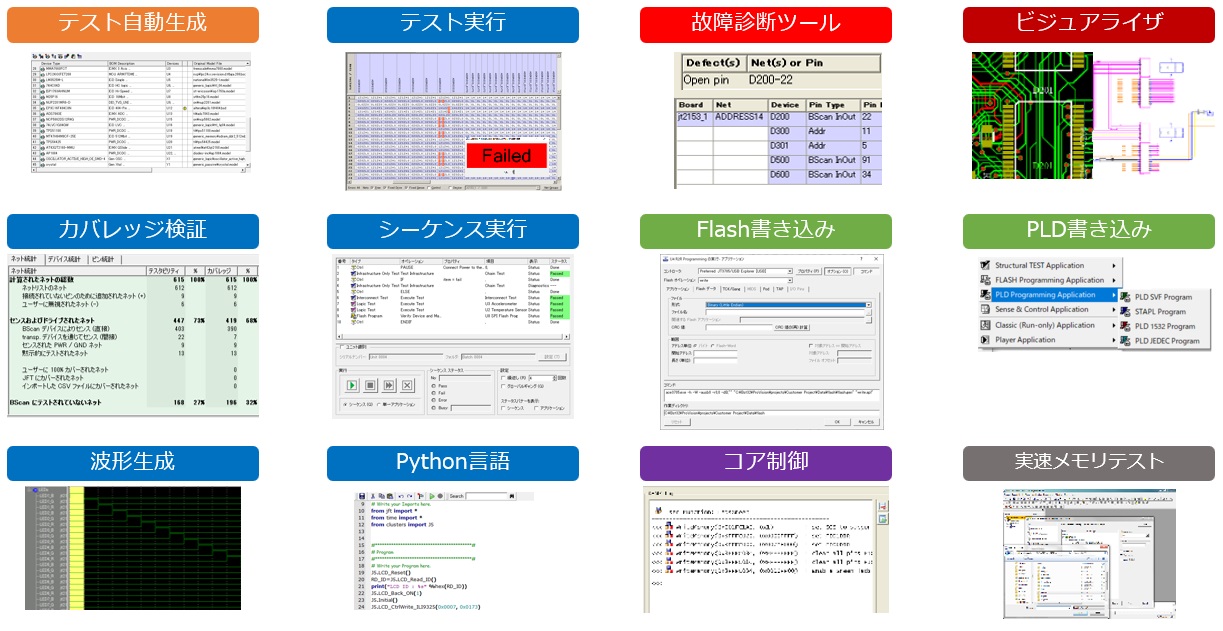

JTAG ProVisionには、基板をテストするためのさまざまな機能があります。図6のように、テスト自動生成機能を中心に、試作基板のテストから量産テスト、メンテナンスまで基板のテストに関する豊富なツールが用意されています。

基本的には自動生成したテストアプリケーションで基板のテストができますが、Python言語を使ってバーチャルプローブから自由に信号を入出力させ、通信コマンドや通信プロトコルを制御するテストアプリケーションを開発することもできます。また、フラッシュメモリやPLDの書き込みを行うこともできます。テストアプリケーションや書き込みアプリケーションは、シーケンス実行ツールに登録すると1クリックで基板のテストから書き込みまで実行できます。このシーケンスを実行した結果は、ログファイルに保存され、基板のシリアル番号と結果のトレーサビリティを管理することができます。

次回予告「JTAGテストのユーザー事例」

今回は開発効率を上げるためのJTAGテストの活用方法をご紹介しました。最大限効果を上げるためには、図研Design Gateway のバウンダリスキャンアドバイザのオプション機能を活用して、DFTサイクルを回し、テストカバレッジを少しでも向上させることが重要になります。テストカバレッジに含まれる回路は、JTAG ProVisionのさまざまなテストとデバッグ機能を使うことができます。特に、測定器ではプロービングできないBGA基板のデバッグに困ったときに、JTAGテストを活用してトラブルを解決することができます。

現在、当社ではJTAGテストに関する新しいWebセミナー「JTAGテストツールのすべて」をはじめました。また、過去に開催したWebセミナーは、動画配信をはじめる予定ですのでお気軽にご参加ください。(https://www.andor.jp/jtag/jtag-webinar/)

次回は、「BGA実装基板の検査の課題を解決したJTAGテストの活用事例」というテーマで、JTAGテストのユーザーにご協力いただき、電子機器の開発・設計、プリント基板の実装・組立・検査を行う製造現場でJTAGテストがどのように活用されているかご紹介します。

第1回 試作基板のBGA部品が動かない!?第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |