第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

2020年05月21日

試作BGA基板6枚中3枚に不具合が発生。どのように解決しますか?

写真1をご覧ください。この試作基板には、BGA部品が2つ実装されていて、FPGAとDDRメモリが使われています。順調に開発が進んでいるかと思ったその時、DDRメモリのデータが化けることが分かりました。それも、試作基板を6枚製造して、3枚に不具合が見つかったのです。皆さまは、この問題をどのように解決するでしょうか?

この基板の不具合解決を難しくしているのは、BGA部品が複数使われているため、測定器で波形を観測できないことと、最近のFPGAにはArmプロセッサが内蔵され高性能化しており、使用方法が非常に複雑になっていることの2点です。今回は、このような試作基板のデバッグとテストを容易にするための設計手法「テスト容易化設計」についてご紹介しましょう。

お客様から伺った不具合解決の体験談

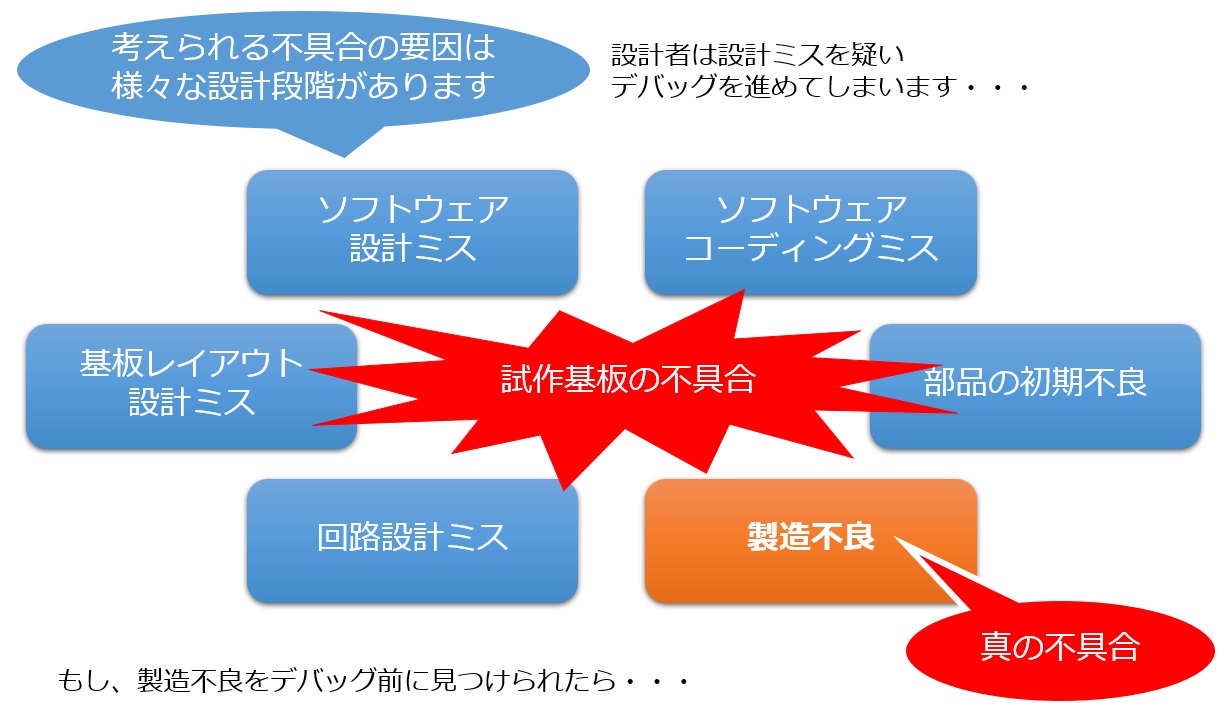

ソフトウェアのデバッグ中にDDRメモリのデータ化けのトラブルが発生しました。最初に疑ったのはArmプロセッサで実行している「ソフトウェア」でした。ソフトウェア開発メンバー全員で「コーディングの検証」「ソフトウェア仕様の検証」「ドライバ仕様の検証」を行いました。大規模なソフトウェアだったため、検証が終わるまで3週間かかり、結果「問題がない」ことを確認しました。

ソフトウェアに問題がないことが分かったため、次にハードウェア開発メンバーに不具合調査を依頼しました。ハードウェア開発メンバー全員で「回路設計の検証」「基板設計、レイアウトの検証」「FPGAロジックの検証」を行いましたが、こちらも「問題がない」ことを確認しました。このとき、すでに不具合発生から6週間が経過していました。

最終的に製造不良を疑い、基板と部品の破損を「目視検査」、はんだの状態を「顕微鏡で確認」、BGAの実装を「X線検査」しましたが、BGA部品は目視検査では見えませんし、X線検査でも確実に実装不良があることを確認することは難しいため、「問題がなさそうだ」という結論になってしまいました。

不具合発生からとうとう7週間が経過してしまいましたが、その原因を突き止めることはできませんでした。そこで、製品開発とは別に、テスト用のFPGAロジックを開発して動作確認を行ってみました。その結果、ようやく製造不良であることを突き止めることができたそうです。

今となっては、「あのときJTAGテストが出来ていれば…」と。

このように、設計者は「設計ミス」を疑いデバッグを進めてしまうため、最終的な「真の不具合」が製造不良であった場合には、設計者の多くの労力がムダになってしまいます。さらに新製品のリリース時期が遅れてしまい、多くの販売機会を失ってしまうかもしれません。

このような試作段階での製造不良をデバッグ前に見つけるためには、JTAGテストが有効なテスト手法となります。このJTAGテストの効率を最大限高めるためには、「テスト容易化設計」を設計段階で考慮することが重要になります。

テスト容易化設計は、DFT(Design For Testability)と呼ばれ、世界中で実践されている設計手法の1つです。特にBGA基板のように高密度化、小型化が進んでいる基板のテストにおいては、回路設計、基板設計段階にテストのことをいかに考慮できるかが、デバッグとテストの容易性を決定します。では具体的に、「テスト容易化設計の5つのポイント」をご紹介します。

●ポイント1.「主要部品選定時にBSDLファイルを入手しましょう」

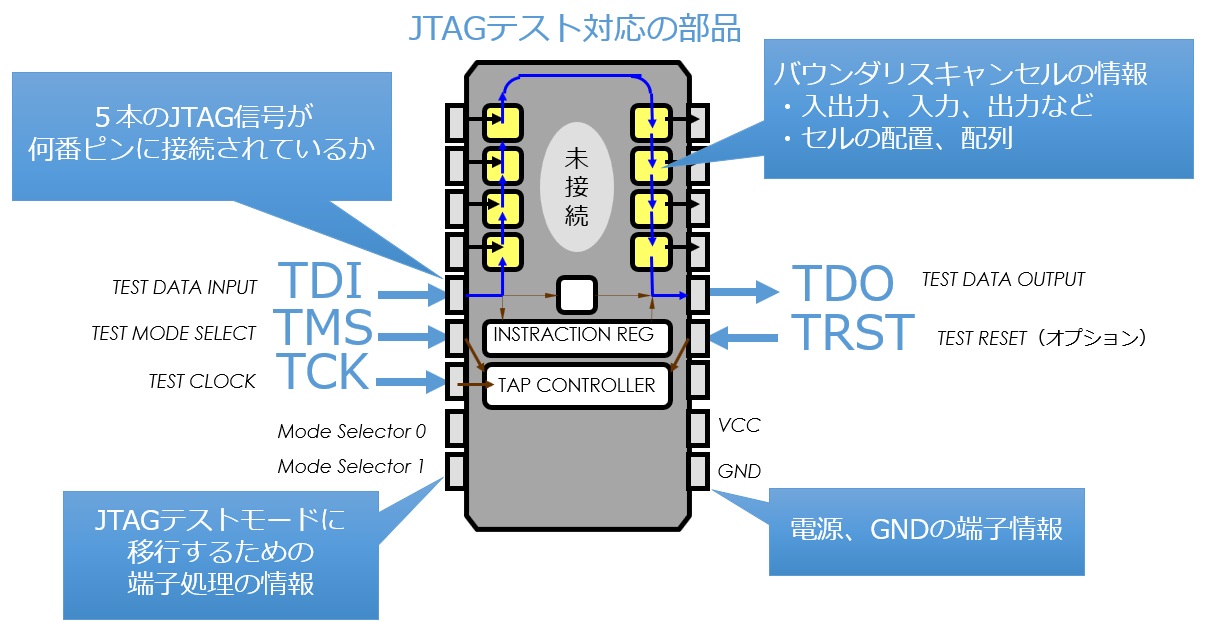

マイコン、プロセッサ、FPGAなどの主要部品を検討する際には、JTAG対応部品(バウンダリスキャン対応部品)を選定することが最も重要になります。JTAGテストに対応した部品であれば、BSDLファイルが入手できます。同じ性能の部品であれば、JTAG対応部品を選ぶことでバーチャルプローブを活かすことができるのです。部品の価格も数ピン増えるだけでは大きく変わりませんし、開発、製造、保守、故障解析などのシーンでテストと解析能力が大きく変わってきますので、トータルのコスト差は考えるまでもありません。

BSDL( Boundary-Scan Description Language )ファイルとは、部品のピン情報、 バウンダリスキャン命令のコードやセルの配置などについて記述されているものです。マイコン、FPGAなどの部品メーカから入手できます。また、JTAGテストモードに移行するための端子処理についても記述されています。もし、BSDLファイルがWebサイトに公開されていない場合には、部品の販売代理店にお問い合わせいただくと入手できることがあります。

●ポイント2.「回路設計上の注意点はBSDLファイルに注目しましょう」

JTAGテストを行うには、部品をJTAGテストモード(バウンダリスキャンモード)に移行するための端子処理が必要になる場合があります。端子処理の有無を把握するためには、はじめにデータシートを確認しましょう。膨大なデータシートの中から必要な情報を探し出すのは大変ですので、以下のキーワード「JTAG」「バウンダリスキャン(Boundary-Scan)」「IEEE1149.1」を検索するとよいでしょう。これでも見つからない場合には、JTAG信号名「TDI」「TDO」「TCK」「TMS」「TRST」で探してみます。

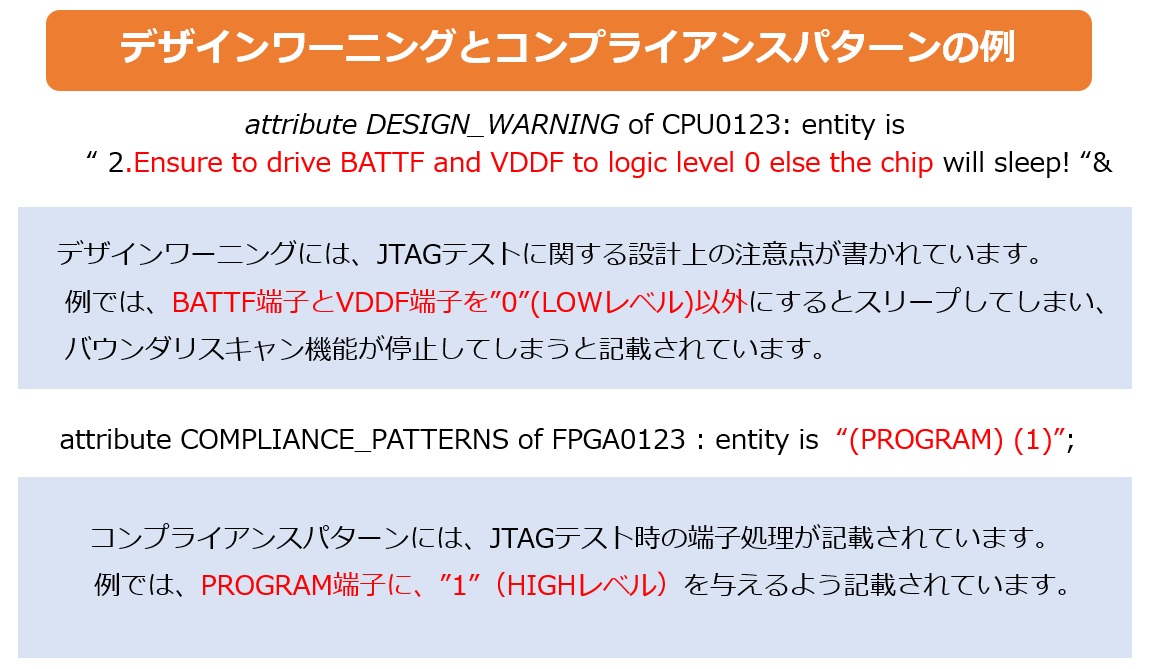

次にBSDLファイルに記述されている設計上の注意点を確認します。BSDLファイルはテキストファイルですので、ダウンロードしたらテキストエディタで開けます。注目するのは、設計上の注意点「attribute DESIGN_WARNING」とコンプライアンスパターン「attribute COMPLIANCE_PATTERNS」というキーワードで、これらは世界標準のIEEE1149.1で定められたものです。また、コメント文にも注意事項が含まれているケースがあります。「IMPORTANT NOTICE」というキーワードなども注意しましょう。

●ポイント3.「JTAG信号の基本回路をチェックしましょう」

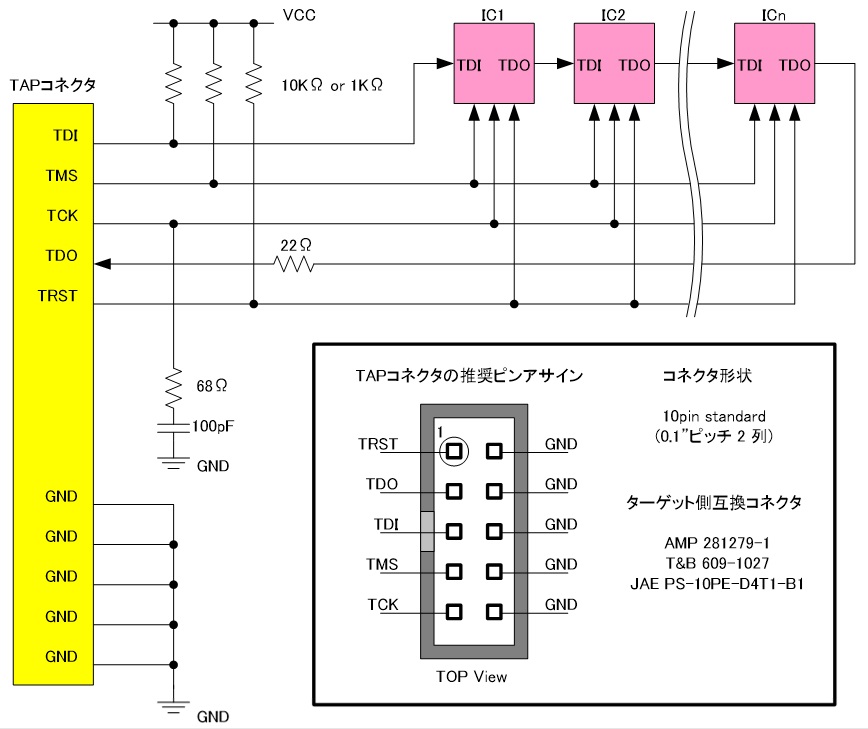

トラブルがあったときに基板をデバッグしようと思っても、JTAG信号が未使用ピンとしてGNDに短絡されてしまっていることがあります。これでは、せっかく部品がもっているテスト機能を活かすことができません。JTAGの5本の信号(TDI、TMS、TCK、TDO、TRST)をアクセスできるようにしましょう。JTAGテストの動作を安定させるために、GNDを複数ピンにアクセスできるようにして、終端処理をすることをお勧めします。終端回路は、部品メーカ推奨のJTAG回路がデータシートに記述されています。特に指定がない場合には、下図のようにJTAGテストツールの推奨回路を参考にします。TAPコネクタは、JTAGコントローラを接続するためのコネクタです。コネクタのスペースがない場合には、テストパッドを設けておいてケーブルをはんだ付けしてもよいでしょう。

●ポイント4.「JTAGチェーンの回路をチェックしましょう」

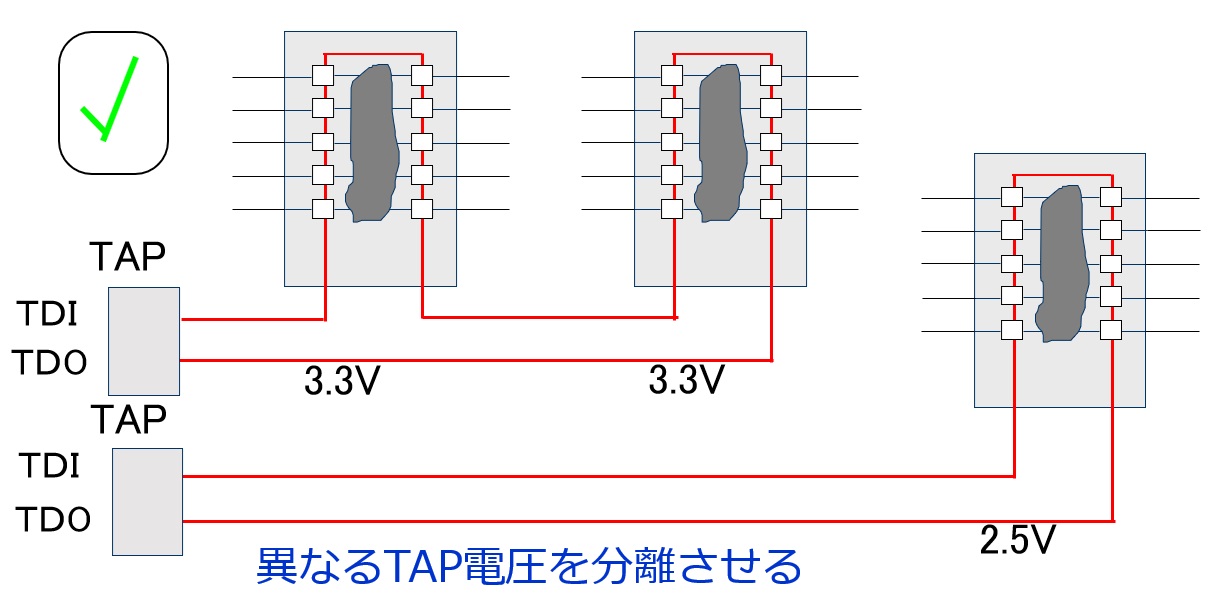

複数のJTAG対応部品を同時に制御するために、シリアル接続することを「JTAGチェーン」と呼んでいます。シリアル接続する際には、TDIとTDOの入出力属性に注意が必要です。また、電圧レベルが異なる部品を同じチェーンにしてしまうと、回路が正しく動作しません。電圧レベルが異なる部品は、別のJTAGチェーンにします。

●ポイント5.「JTAGの非同期回路を制御してテスト範囲を拡大しましょう」

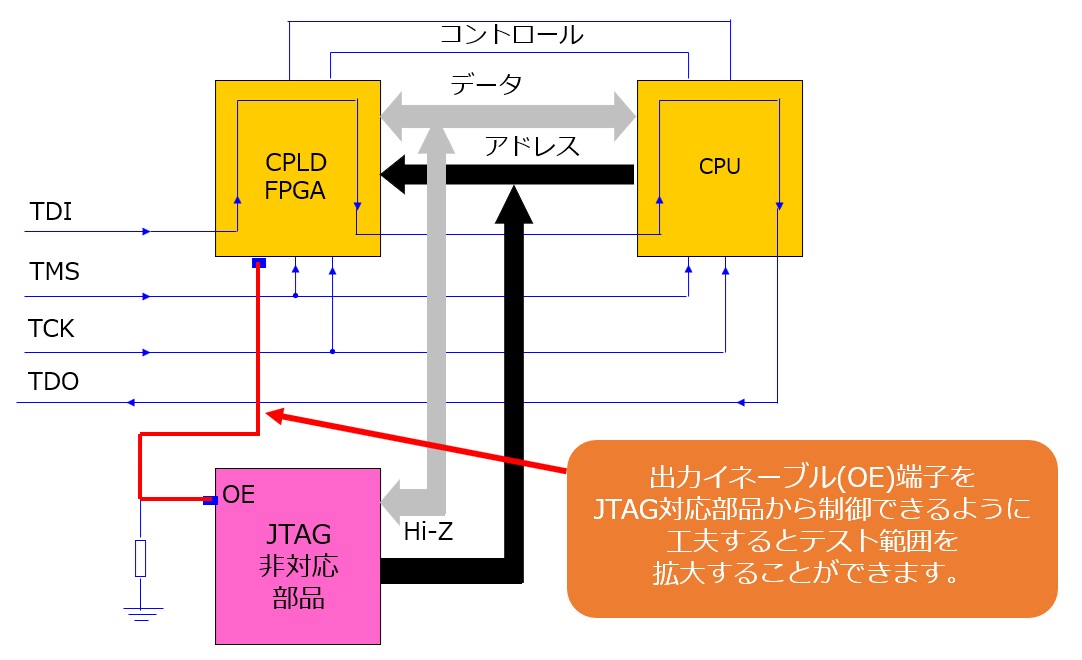

JTAGテストは、複数のJTAGテスト対応部品のテストクロック(TCK)を使って、同期をとりながら信号の入出力をさせてテストする仕組みです。JTAGテスト範囲を拡大するためには、非同期となってしまうJTAG非対応部品の出力競合を抑える必要があります。

次回予告 「テスト範囲を最大化する。DFTサイクルとは」

今回ご紹介したテスト容易化設計 DFTの5つのポイントを実践することにより、確実にモノづくり後のデバッグを効率的に行うことができるようになります。これからデザインレビューを行う機会に思い出していただき、トラブルがあったときにJTAGテストが出来るようにしておくことをお勧めします。

弊社のWebセミナーでは、テスト容易化設計に関するご説明と国内のJTAGユーザの設計者、生産技術者、故障解析の担当者からインタビューした生の声をご紹介しています。無料でご参加いただけますので、お気軽にご参加ください。(https://www.andor.jp/jtag/jtag-webinar/dft/)

次回は、「DFTサイクル」というキーワードで、図研の回路図CAD である「CR-8000 Design Gateway」と JTAGテストツール「JTAG ProVision」の間で、どのようにテスト容易化設計を実現するかをご紹介します。

第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |