第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

2020年04月23日「.ccfファイル」から基板テスト用のデータが自動生成できることを知っていますか?

「JTAG(ジェイタグ)」という言葉を聞いたことがあると思います。ソフトウェアエンジニアにとっては、Armマイコンのソフトウェア開発用 「JTAG ICE(デバッグプローブ)」が身近でしょうし、ハードウェアエンジニアは恐らく、「FPGAやフラッシュメモリの書き込み」のJTAGを思い浮かべるでしょう。

しかし本来、JTAGはデバッグや書き込み用だけに使うものではありません。「本来のJTAG」は、試作基板のデバッグ期間を短縮する目的で、ネットリスト「.ccfファイル」を使い、BGAのはんだ不良を見つけるために使うものなのです。では、「本来のJTAG」とはどのようなものなのでしょうか?今回は、JTAG誕生の歴史と仕組みについてご紹介しましょう。

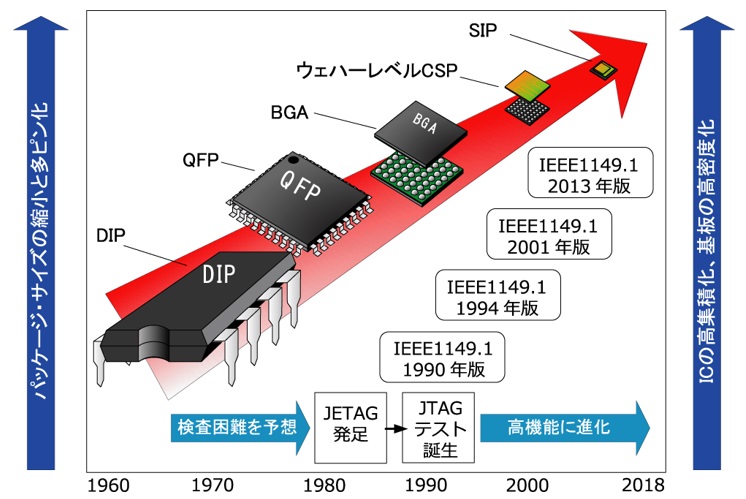

部品パッケージの進化

はじめに、部品パッケージの進化を見てみましょう。1960年代にDIPパッケージから始まり、電子機器の小型化と高性能化が進む中で、QFPパッケージが市場に広がっていきました。DIP部品やQFP部品は、基板に実装した後でも、目視や顕微鏡ではんだ付けの状態を確認することができました。したがって、部品のはんだ付けに問題があったとしても、比較的容易に不良箇所を特定することができました。

部品のパッケージが大きく変化したのは、1990年のBGA(Ball Grid Array)パッケージの誕生からです。部品の裏面にはんだ付けをするためのボール状の端子があるため、BGA部品を基板に実装してしまうと、はんだ付けをした状態を目視では確認することができなくなってしまったのです。そのため、将来BGAパッケージの部品が市場で使われるようになったときに、どのようにテストするかが電子機器業界にとって大きな課題となり、当時は「テストクライシス(テストの危機)」というキーワードが流行しました。

バウンダリスキャンテスト IEEE1149.1規格の誕生

1985年にヨーロッパの先端企業を中心として、BGA基板のテストクライシスを解決するために立ち上がった業界団体が「JETAG (Joint European Test Action Group)」です。1986年には米国の企業が加わり、「JTAG (Joint Test Action Group)」という団体名に変わり、次世代の部品パッケージの検査方法に関する検討が進みました。

この団体が中心となり、1990年にBGAパッケージと狭ピッチのQFPの部品を含む高密度実装基板のテスト手法である、「バウンダリスキャンテスト アーキテクチャ」 (Boundary Scan Test Architecture) をIEEE 1149.1として規格化しました。バウンダリスキャンテストは、「JTAGテスト (海外ではJTAG Testing)」とも呼ばれています。この連載では、「JTAGテスト」と呼ぶことにします。

試作基板の受入検査で使えるJTAGテストの仕組み

BGA基板のデバッグ効率をあげるためには、試作基板の受入検査でJTAGテストを活用して、モノづくりに問題がない旨の確認をお勧めしています。JTAGテストの大きなメリットは、マイコン用のテストプログラム開発やFPGAのロジック開発などをせずに基板のテストができることです。ソフトウェア、FPGAのロジックをデバッグする前に、モノづくりに問題がないことを確認できるので、設計のデバッグに注力することができます。

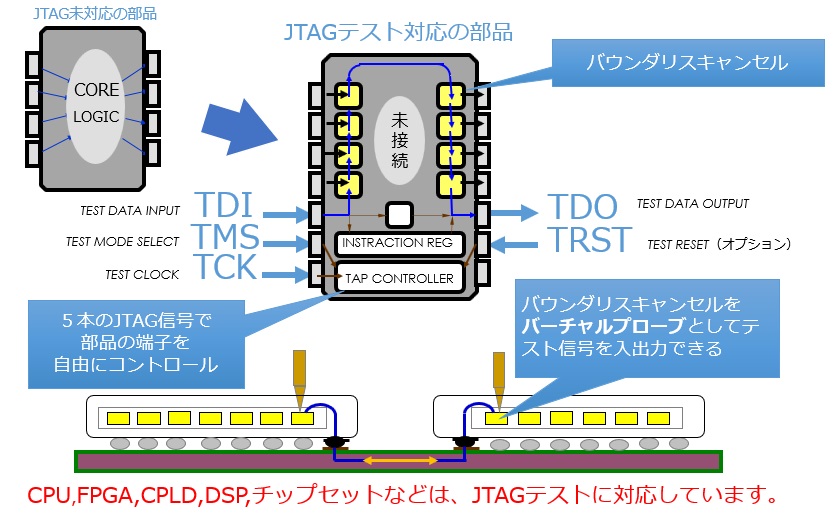

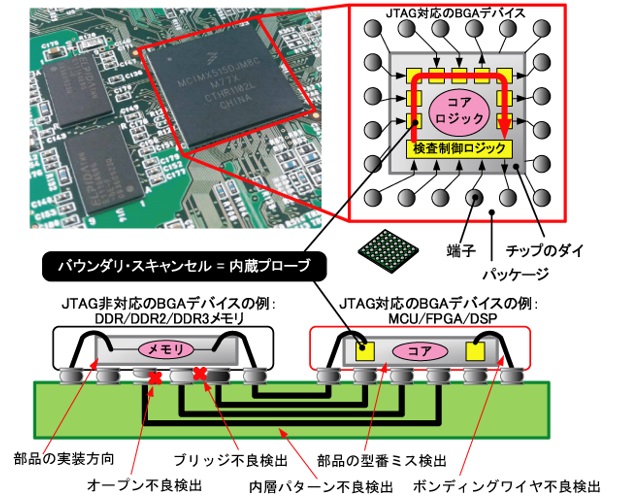

JTAGテストは、TAP(テストアクセスポート)である5本のJTAG信号(TDI、TDO、TMS、TCK、TRST)を利用して、JTAGテストに対応した部品をPCから自由にコントロールできる仕組みです。JTAGテスト未対応の部品とJTAGテスト対応の部品とを比べると、部品が持つ本来のコアロジックと部品の端子との間に、バウンダリスキャンセル(Boundary Scan Cell)という信号を入出力させるためのロジックが追加されていることが分かります。バウンダリは日本語で「境界」ですので、コアロジックと部品の端子との境界をスキャンするという意味になります。

このようにJTAGテストとは、バウンダリスキャンセルを制御して、部品の端子をプローブピンとして通電試験ができるテスト手法です。テスト中はJTAGテスト対応部品のコアロジックが切り離され、部品の端子から自由に信号を入出力することができます。実は、このテストの仕組みは、皆さまが使用しているほとんどすべてのFPGAが対応しているのです。使わない手はないですよね?

どのようなモノづくりの不具合が見つかるのか

いま開発現場で問題となっている基板の多くは、BGA部品を実装した基板です。そうした基板の多くは、JTAG対応のマイコン、FPGA、PLDとJTAG非対応のDDRメモリという構成になっています。JTAGテストを使うと、JTAG対応のBGA部品の端子に内蔵されたバウンダリスキャンセルを利用して、JTAGテスト非対応のDDRメモリに対し、メモリの制御信号、アドレス信号、データ信号を制御して、メモリを読み書きするテストを行うことができます。

このように、JTAGテストによって見つけられるBGA基板の不具合には、「はんだ不良(オープン不良、ブリッジ不良)」、「プリント基板のパターン不良(断線、ブリッジ)」、「部品内部のボンディングワイヤの断線」、「部品の型番違い」、「実装方向のミス」などがあります。JTAGテストは、測定器では確認できない不良を検出できることから、近年の高密度実装基板に対する有効なテスト手法の一つとして注目を集めています。

JTAGテストツールとCR-8000 Design Gateway の連携

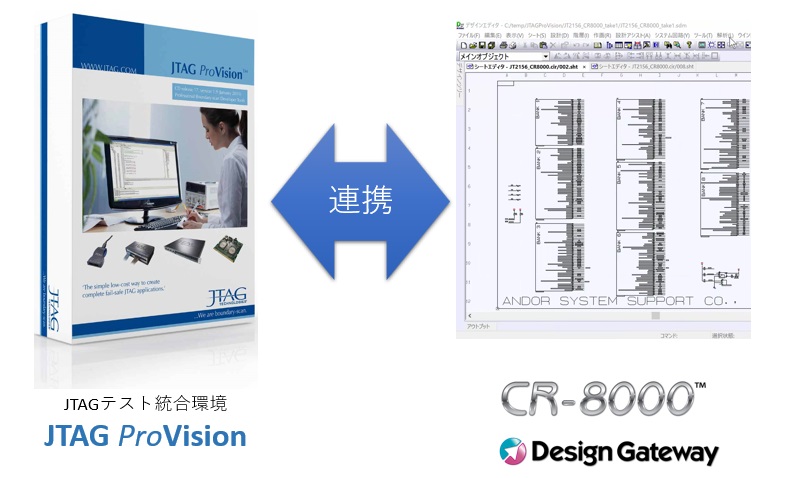

JTAGテストの規格が誕生した1990年から約15年間は、JTAGテストツールが成熟しておらず、JTAGテストパターンを準備するためには、ユーザがテスト対象の回路図を読み解きながら、テキストエディタを使用して手作業でテストパターンを作り込む必要がありました。テストの担当者は回路設計者と同様に回路を理解することが求められ、JTAGテストを導入した企業では、専任の技術者を育成する必要がありました。そのため、JTAGテストを導入したものの、継続して使っていくことが困難な時代もありました。

しかし、この状況はJTAGテストツールの進化により一変しました。オランダのJTAG Technologies社が、2005年にテストパターンの自動生成機能を大幅に拡張したJTAGテストツール「JTAG ProVision」をリリースし、誰でも簡単にJTAGテストパターンを生成できるようになりました。さらに、図研の回路図CAD であるCR-8000 Design Gatewayと連携できるようになって、より回路設計者の方にも使いやすく進化を遂げました。ツール間の連携機能については、次回の連載でご紹介したいと思います。

JTAGテストパターンに必要なファイル

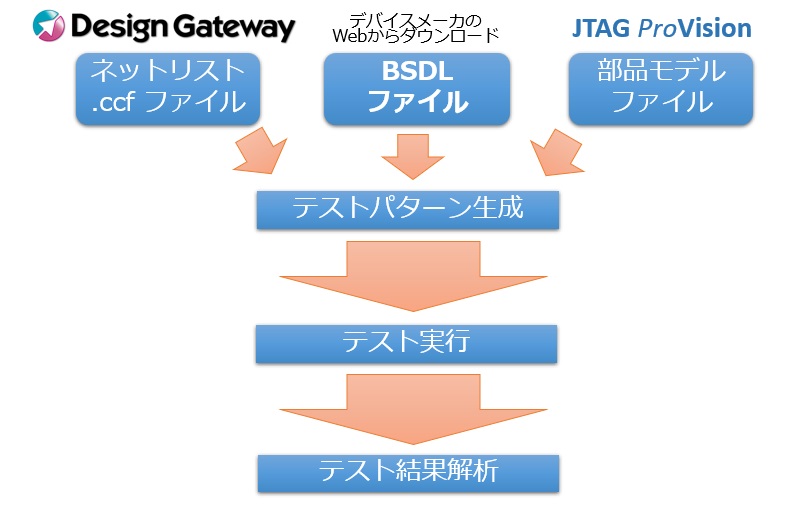

JTAG ProVisionを用いると、基板を製造するために使用するネットリスト「.ccfファイル」(回路図CAD CR-8000 Design Gateway から生成される配線情報)とJTAG対応部品のテスト回路情報が記載されている「BSDLファイル」(デバイスメーカより提供されるファイル)、JTAG非対応部品の「部品モデルファイル」(JTAG ProVisionに内蔵されている部品の真理値データ)からJTAGテストパターンが自動生成されます。

BSDLファイル(Boundary Scan Description Language)とは、JTAG対応部品にどのようなバウンダリスキャン用の回路が内蔵されているかを記載したものです。このBSDLファイルには、JTAG対応部品のバウンダリスキャンセルをコントロールするための情報が記載されており、JTAGテストを実行する際には必須となる重要なファイルです。

JTAGテストによるBGA基板のテストカバレッジ

では、どのようなテストが自動生成されるのかご紹介しましょう。JTAG ProVisionには、2020年4月時点で28万種類の部品モデルファイルが用意されています。このライブラリから自動生成されたJTAGテストパターンは、バウンダリスキャンセルを使って、基板全体の回路を制御して、部品モデルファイルの期待値と比較しながら合否判定が行われます。

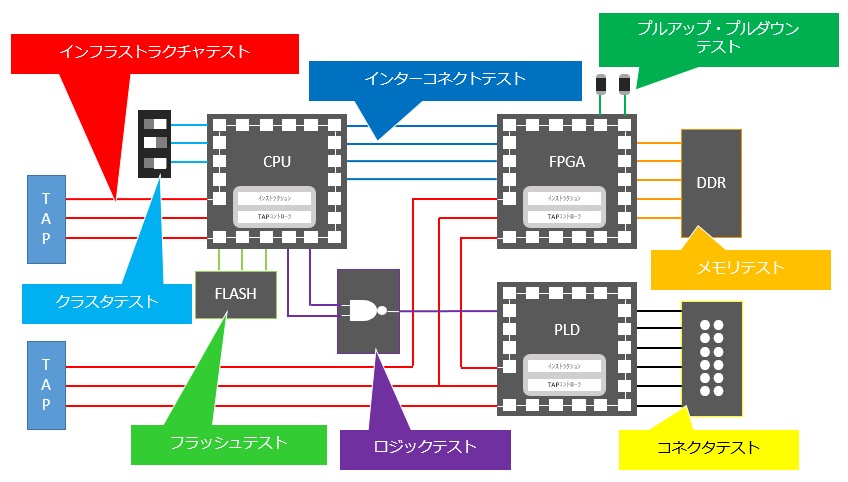

「インフラストラクチャテスト」ですが、基板に正しく通電されているか、JTAG信号に不良がないか、正しい部品が実装されているかを、JTAG対応部品のID番号を照合してテストすることができます。このテストに問題がなければ、JTAGテストを実行するためのインフラが準備できたことになります。次に実行するのは、JTAGテストのメインである「インターコネクトテスト」です。JTAGテスト対応部品間の配線とはんだ不良の有無をテストできます。

その他のテストは、JTAGテスト非対応の部品向けのもので、「プルアップ・プルダウンテスト」「メモリテスト」「コネクタテスト」「ロジックテスト」「フラッシュテスト」「クラスタテスト」などがあります。以前からJTAGテストを知っていた方の中には、JTAG対応部品間のインターコネクトテストしかできないと誤解されている方も多いようですが、JTAGテストツールの進化によりテストカバレッジは劇的に向上していることがお分かりいただけます。

次回予告 「BGA基板のデバッグで困らない。テスト容易化設計とは」

今回は、JTAGテスト規格とJTAGテストのアーキテクチャ、それからテスト生成方法をご紹介しました。試作基板にBGAが搭載されているときに、測定器で触れない代わりにJTAGテストが使えることがお分かりいただけたかと思います。少しずつ「本来のJTAG」の使い方が見えてきたのではないでしょうか。

JTAGテストのアーキテクチャについて、詳しく知りたい方は「JTAG技術レポート」という小冊子をお届けしますのでお申込みください。(https://www.andor.jp/jtag/download/jtag-report/)

また、Webセミナーでは、JTAGテストの入門編、成功事例編、設計者向けなどを開催しています。CR-8000 Design Gatewayとのツール連携についても解説しています。(https://www.andor.jp/jtag/jtag-webinar/)

次回は、BGA部品を使った試作基板のデバッグで困らないために、どのようなことを注意すべきか、CR-8000 Design Gatewayを活用したテスト容易化設計についてご紹介します。

第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |