第4回 テスト範囲を最大化する「DFTサイクル」とは

2020年07月02日

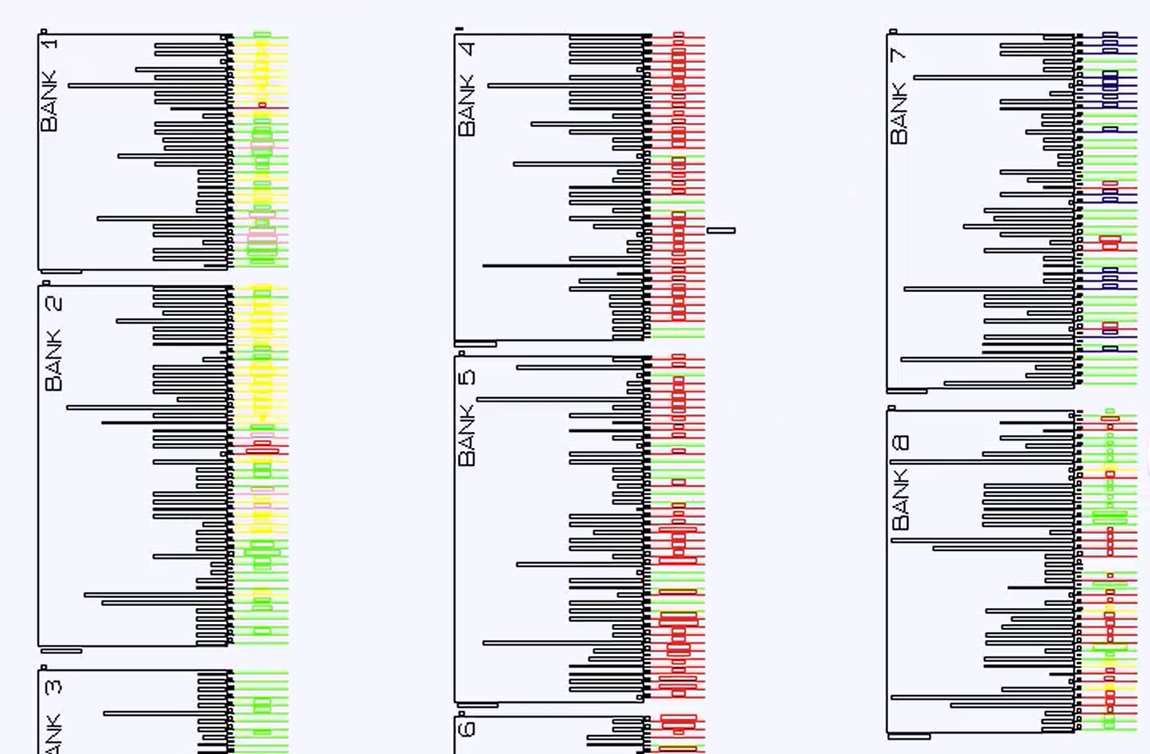

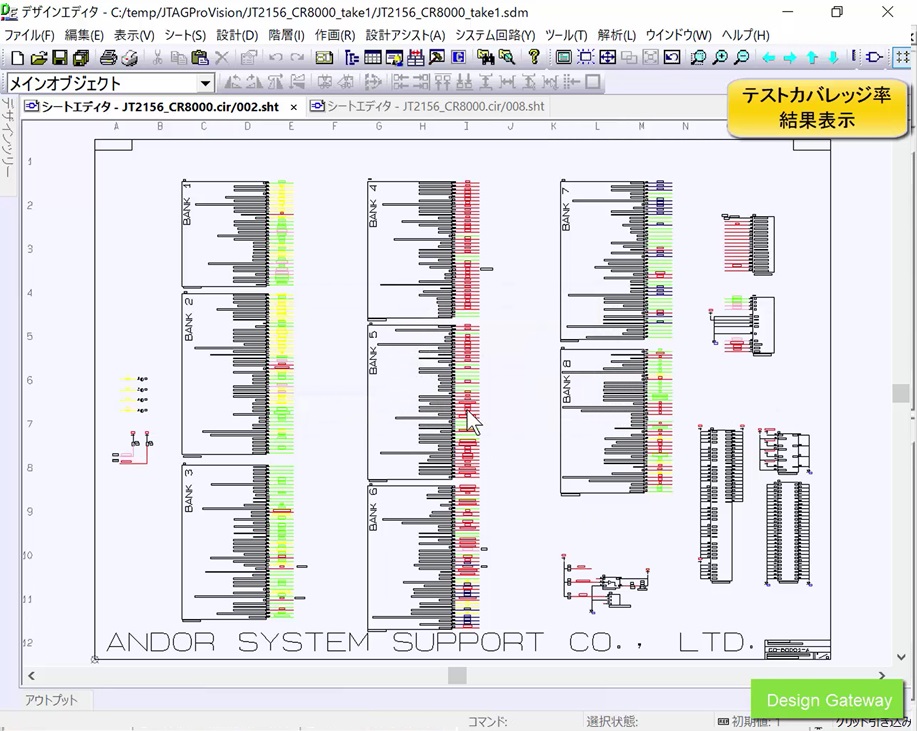

回路図の色は何を意味しているかわかりますか?

回路図のFPGAのI/Oピンにマーキングされた色は、何を意味しているか分かりますか?

これはデザインルールチェックの結果ではありません。回路設計者の方は、「製品の性能」や「製造コスト」などを考えながら回路設計を行っているかと思いますが、もう1つ重要な考慮すべきポイントがあり、その内容がこのマーキング結果に示されています。

実は、マーキングされた結果は、製造テストを行う際の「テストカバレッジ」を示しています。意外な事実ではありますが、回路設計段階では量産時のテスト方法が考慮されていないケースが多いことが最近分かってきました。BGA部品を実装した製品の量産テストの直前になって、テストパッドがないためにどのようにテストをしたらよいか悩まれている現場を目にすることがあります。

テストカバレッジという言葉は、ソフトウェア開発の世界では一般的になってきました。しかし、ハードウェア開発の世界では、「製品の性能」や「モノづくり」「製造コスト」などという視点が中心となっており、「テストカバレッジ」という視点でデザインレビューを行うことが、まだ一般的になっていない印象を受けます。

設計部門と製造部門とのコミュニケーションが設計初期の段階で取られている企業はよいのですが、多くの場合は試作基板のデバッグが終わった後で、ようやく量産のテストについて検討が始まるというのが実情のようです。量産直前になって、テストのために回路変更や基板設計変更などということは通常できません。ですので、量産のときに困らないためにも、今回ご紹介する「DFTサイクル」を参考にしていただけると嬉しいです。

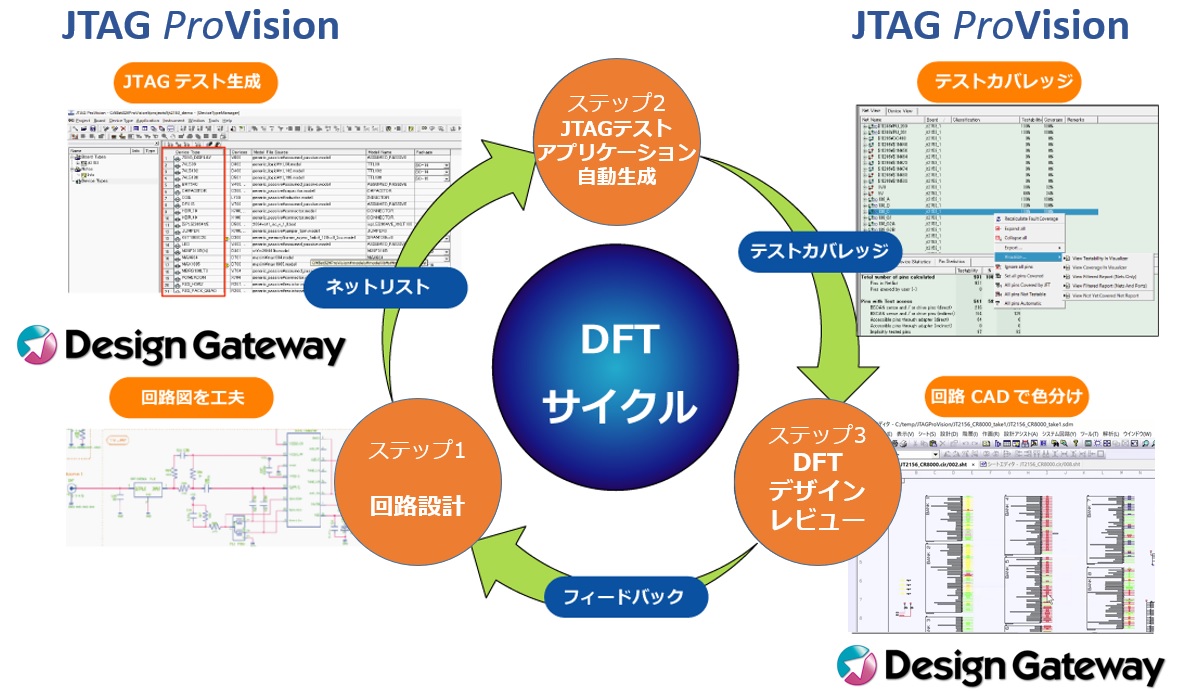

3つのステップから構成される「DFTサイクル」

下図がDFTサイクルのイメージです。DFTサイクルのステップ1は、「回路設計」です。ステップ2は、「JTAGテスト生成」です。JTAGテストツール 「JTAG ProVision」の28万種類の部品モデルファイルを使い、ウイザード形式でテストアプリケーションを自動生成させることができます。ステップ3は、テスト容易化設計のデザインレビュー「DFTデザインレビュー」です。このテスト容易化設計のためのDFTサイクルを回すことが、皆さまの製品の品質を向上させるとともに、製品開発の効率化への近道となります。

では、実際のツールでは、どのような手順でDFTサイクルを行うのか、「JTAG ProVision」と回路CAD「Design Gateway」、そしてそのオプションの「バウンダリスキャンアドバイザ」との連携機能について、ステップ毎にご紹介しましょう。

ステップ1:テスト容易化設計を考慮した回路設計

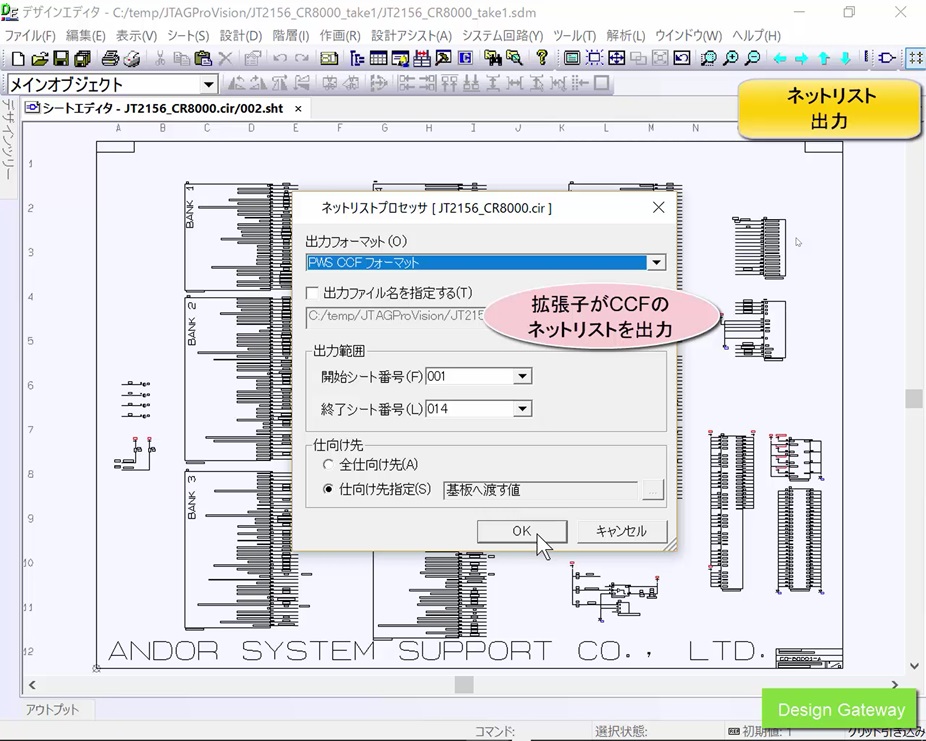

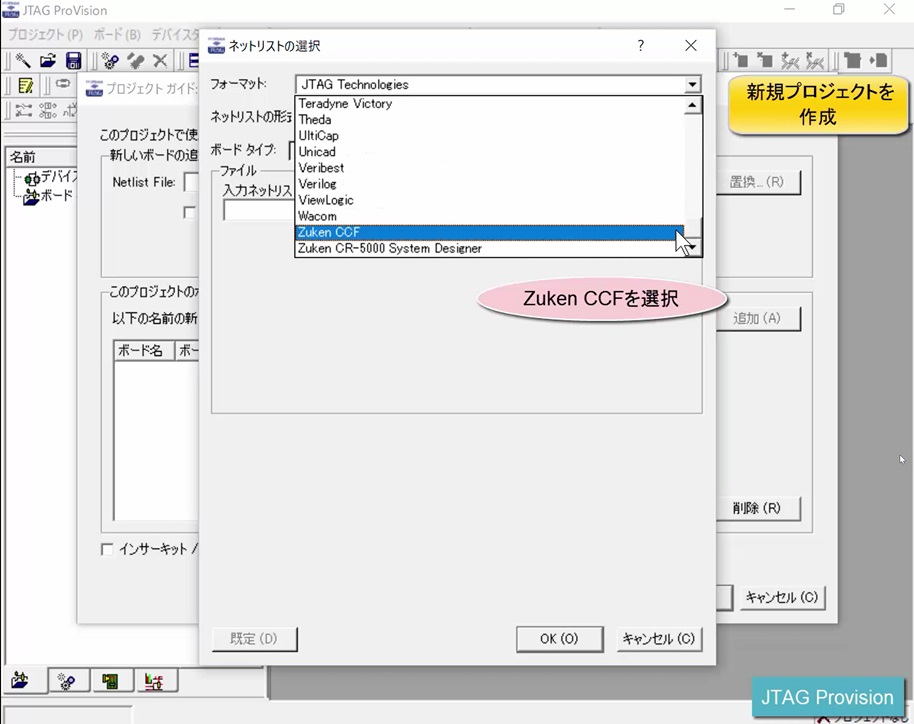

最初に、試作基板の設計段階で、テスト容易化設計を考慮した回路設計を行います。前回の連載第3回でご紹介したように、試作基板の回路設計時に「テスト容易化設計の5つのポイント」を押さえた上で、JTAGテストを行うためのインフラを整えることが重要になります。試作基板の回路図が完成して、デザインレビューを行う前に、ネットリスト「ccfファイル」を出力します。通常ccfファイルは、ボード設計を行うために使用されますが、今回はボードテストを行うためのJTAGテストアプリケーションを自動生成する目的で使用します。

ステップ2:JTAGテストアプリケーションを自動生成する

JTAG ProVisionでは、テストアプリケーション生成のウイザードに沿って、テストアプリケーションが自動生成されます。実際のテスト生成手順をご紹介しましょう。

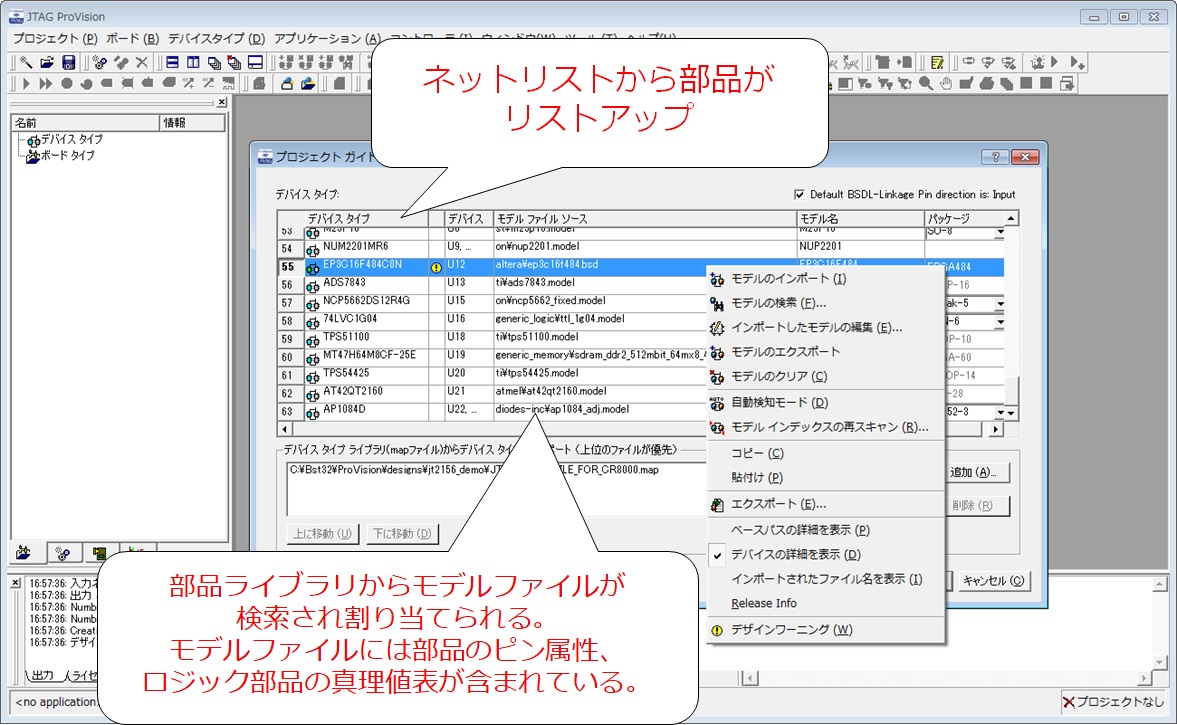

はじめに、テスト対象基板のネットリストをインポートします。ネットリストには、回路図中の部品番号と型番、部品間の配線情報が含まれています。

次に、テスト対象の基板に使われる部品がどのように動作するかをJTAGテストツールに認識させます。回路図上の部品の型番に対応するJTAGテストツールの部品ライブラリを選択します。回路上の部品名が、メーカの型番になっていれば、型番で検索して候補となる部品から選択します。回路図の部品名が購買コードになっている場合には、部品表を参照しながら部品の検索を行います。

JTAG ProVisionには、2020年5月末時点で28万種類の部品ライブラリが用意されています。この部品ライブラリには、部品の内部ロジックの情報、端子の入出力属性が含まれています。部品ライブラリには抵抗やコンデンサなどの情報も用意されており、信号を出力するときに、出力信号が競合してしまい部品を破損させないか、電源やGNDに対して信号を出力させて破損させないかなどをJTAGテストツールが自動的に判断して、安全なテストアプリケーションを自動生成するために使用されます。

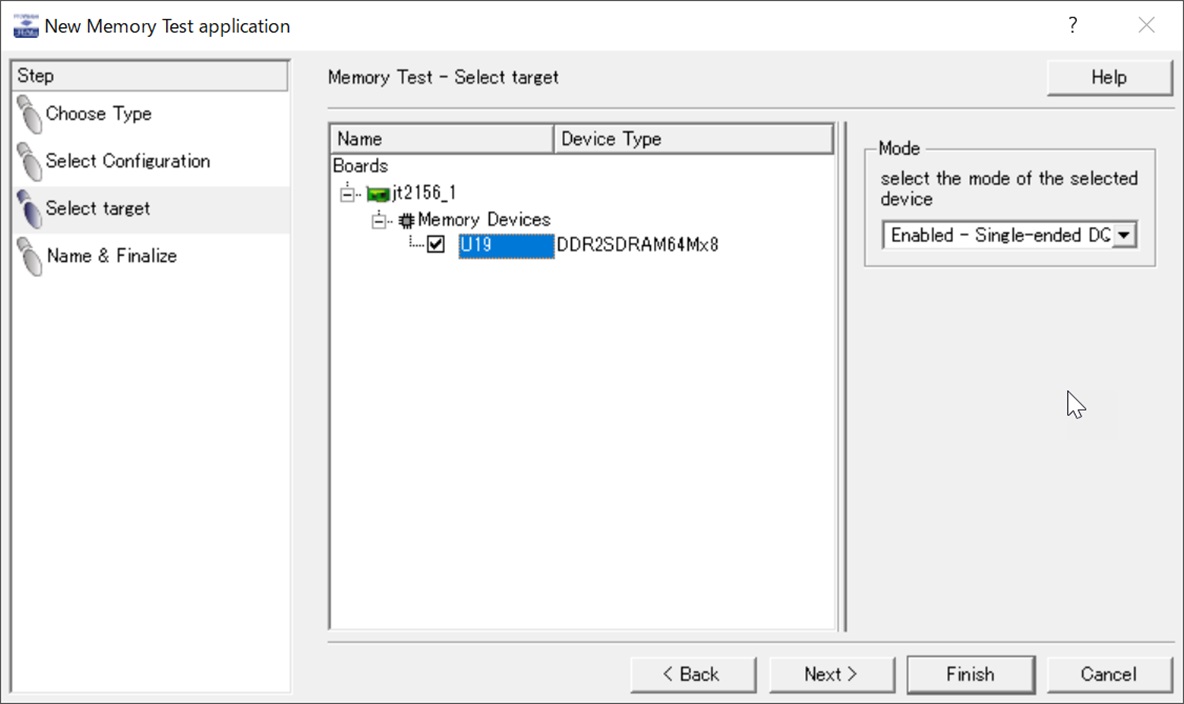

部品ライブラリの設定が終われば、テストアプリケーションを簡単に生成できます。連載の第2回でご紹介した「インフラストラクチャテスト」「インターコネクタテスト」「プルアップ・プルダウンテスト」「メモリテスト」「コネクタテスト」「ロジックテスト」「フラッシュテスト」「クラスタテスト」です。例えば、DDRメモリのテストアプリケーションを生成する場合には、基板上に実装されているメモリの一覧から、テストしたいメモリを選択するだけでテストアプリケーションが自動生成されます。テストプログラムを開発することを考えると、圧倒的に短い時間でボードテストの準備が整います。

ステップ3:テスト容易化設計「DFTデザインレビュー」を行う

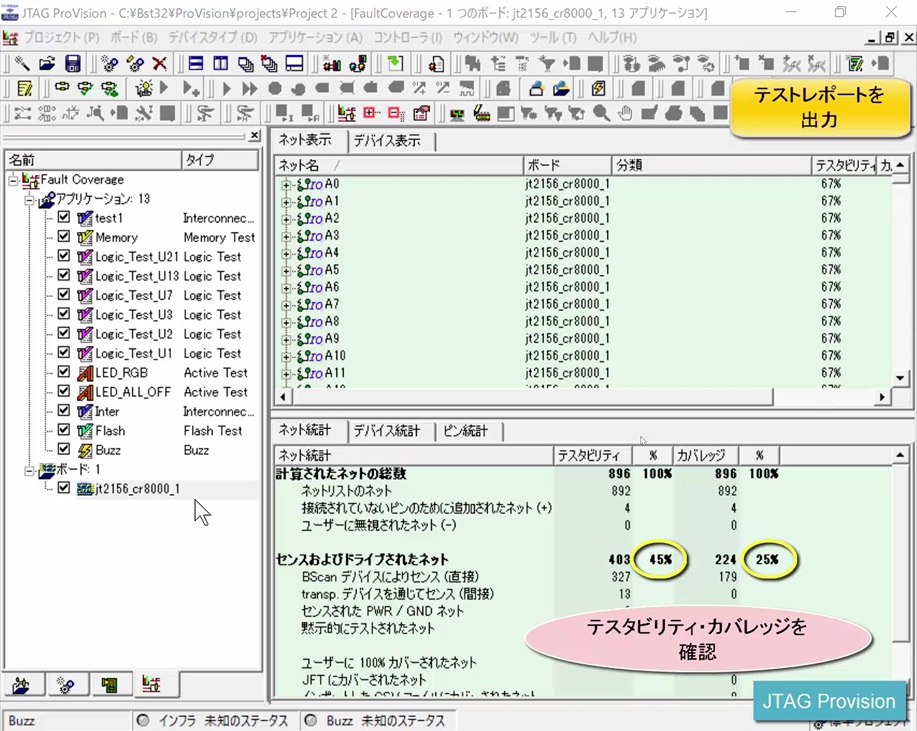

自動生成したテストアプリケーションの一覧から、使用するテストアプリケーションすべてにチェックするとテストカバレッジ情報が生成されます。テスタビリティは、検査治具やコネクタテスト用のケーブルを準備した場合におけるテストの可能性を示しています。もう1つ表示されるテストカバレッジは、基板単体でテストできる範囲を示しています。例えば、試作基板の受入検査で、検査治具がない状況やコネクタに接続するケーブルもない状況などでは、テストカバレッジの情報が参考になるでしょう。

Design Gatewayのオプション「バウンダリスキャンアドバイザ」機能を使うと、JTAG ProVisionで生成したテストカバレッジとテスタビリティの情報をDesign Gatewayの回路図にマーキングすることができます。マーキングされているネットは、JTAGテストで実装テストができることを意味し、逆にマーキングされていないネットは実装テストができないことを視覚的に捉えることができます。回路設計者は、このテストカバレッジの情報からモノづくりをする前にデザインレビューすることができます。このデザインレビューのことを、DFTデザインレビュー(テスト容易化設計デザインレビュー)と呼んでいます。

DFTサイクルを回して設計品質を向上

DFTデザインレビューの結果、テストカバレッジが低い場合には、基板製造前に回路を工夫することでテストカバレッジを改善することができます。具体的な対策としては、ピンアサインの変更、未使用ピンの利用、部品の変更などさまざまな方法があります。また、検査治具や検査用のケーブルの情報を回路図に付加することにより、テストカバレッジを改善することもできます。

ステップ1に戻り、修正した回路図からネットリストを出力して、ステップ2のテスト生成、ステップ3のDFTレビューというDFTサイクルを繰り返します。このDFTサイクルを繰り返すことにより、基板製造前に品質の向上と検査コストの削減、開発期間短縮による開発コストの削減を確実に実現することができます。特にプローブピンを使用できない高密度な基板においては、DFTとテストカバレッジのレビューが製品のライフサイクルにおける品質向上とコスト削減、直行率の改善を成功させるポイントになります。

次回予告「BGA基板のテストパッド削減とデバッグに役立つテストツールの活用例」

JTAGテストを導入して成功している企業では、製品の設計段階で「DFT(テスト容易化設計)」を実践することがルール化されています。デザインレビューの項目の1つに「DFT」というキーワードを挙げて取り組まれているのです。最大限にJTAGテストを活用できる環境が整うと、「BGA実装不良基板の市場流出防止」だけではなく、「開発期間の短縮」「検査準備の工数削減」「検査時間の短縮」「故障解析の工数削減」「製品品質の向上」など、設計から製造、保守までのすべての製品ライフサイクルでメリットが得られます。これにより、試作基板の設計段階からDFTを実践することが、企業全体の利益に直結することがわかります。現在、当社ではJTAGテストに関するWebセミナー「JTAGテスト容易化設計セミナー」「JTAGテスト成功事例セミナー」などを無料で開催していますので、お気軽にご参加ください。(https://www.andor.jp/jtag/jtag-webinar/)

次回は、DFTサイクルを実践すると、BGA基板のテストパッドがどれだけ削減できるのか、回路設計者がデバッグのときにどのようなメリットを得られるのか、テストツールの機能などをご紹介します。

第1回 試作基板のBGA部品が動かない!?第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |