第1回 試作基板のBGA部品が動かない!?

2020年03月26日

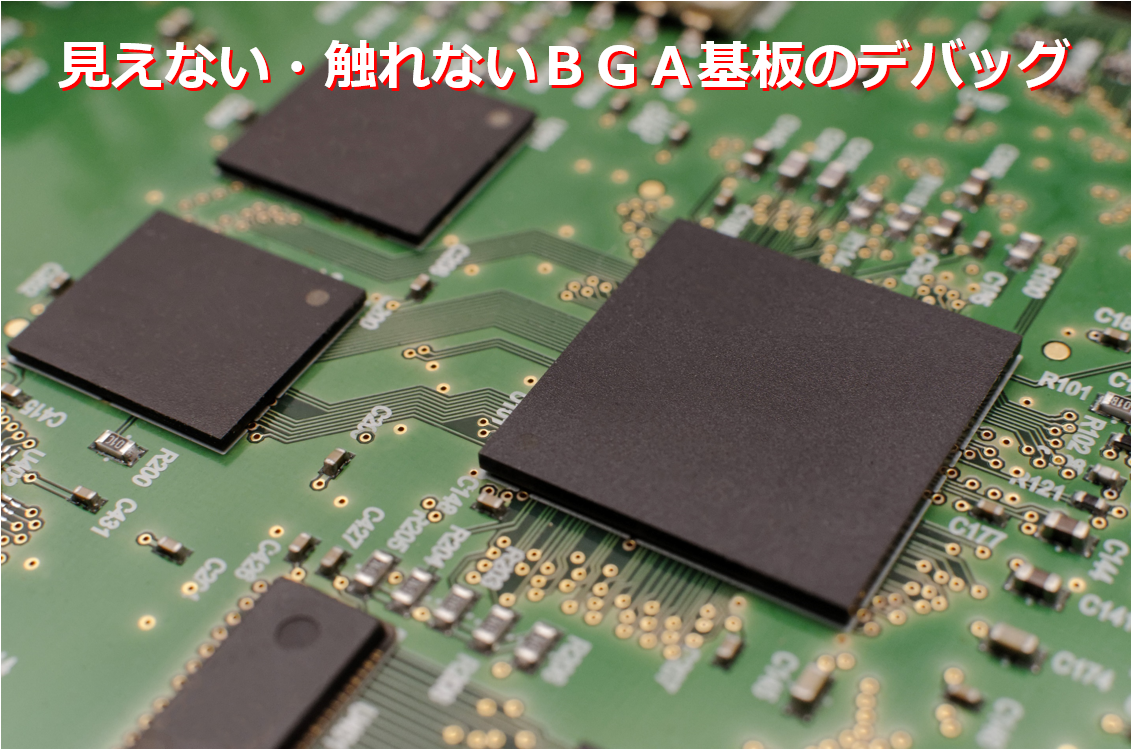

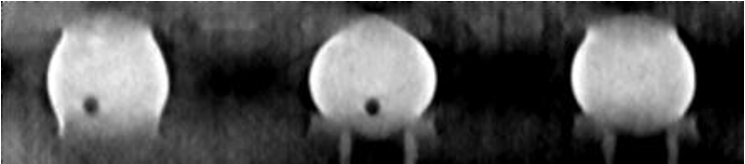

突然ですが、なんの写真か分かりますか?

はじめまして、「Club-Z」で連載を担当させていただきますアンドールシステムサポートの谷口です。こちらのコラムでは、試作基板のデバッグやテストにおける課題と解決策についてお話ししたいと思います。少しでも皆さまの業務を見直すきっかけにしていただけると嬉しいです。

早速ですが、写真1は3次元X線の画像です。これが、何を示しているか分かりますか?

実は、BGAパッケージの部品にはんだ不良があることを示しているのです。3つのボールが並んでいますが、中心のボールには、はんだが接合していないことが分かります。白く見えているのは金属ですが、左右のボールは部品側(上部)と基板側(下部)に正しくはんだが接合していることが分かります。しかし、中央のボールは、部品の端子のまま球状に見えるため、はんだが接合していないことが分かります。

最近、このようなBGA部品のはんだ不良が増えているのです。

試作基板の実装トラブルが増えている!?

電子機器の小型化と高性能化が進んでいることは、多くの方が実感されているのではないでしょうか。実装技術が進化することにより、電子部品も小型のパッケージが増え、基板のサイズも年々小さくなっています。FPGA、プロセッサ、メモリなどの基板を構成する主要部品の小型化で、BGA部品が一般的に使われるようになりました。

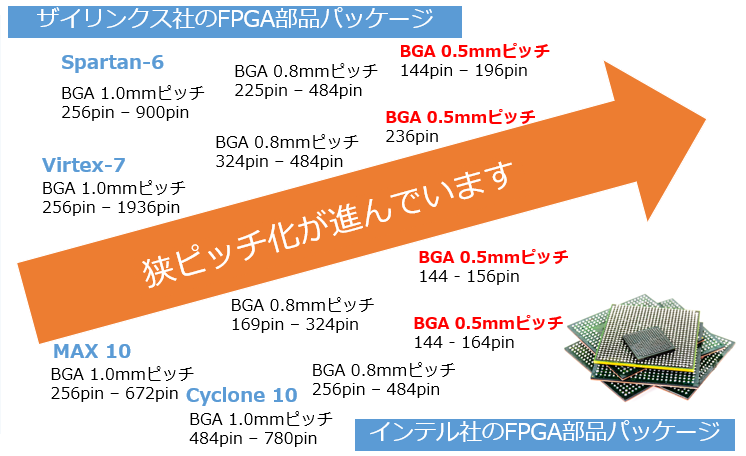

BGA部品のパッケージは、ボール間のピッチが1.27mmから1.0mm、0.8mm、0.5mmと年々狭くなってきています。ザイリンクス社とインテル社で、さまざまな業界の製品で使われているFPGAを調べたところ、下記のように小型製品向けの狭ピッチの部品パッケージが用意されていました。

従来、BGAパッケージ部品の実装は、はんだ不良が少ないと言われてきました。しかし、これは3年ほど前までの話だったようです。BGAの狭ピッチ化にともなって、この数年間で不良基板が増えており、お問い合わせいただく件数が増えているのです。

お客様の故障解析をサポートする中で気付いたことは、0.5mmピッチの狭ピッチBGAを使い始めると、極端に実装不良が増えるということです(写真1のBGAが、まさに0.5mmピッチです!)。トラブルの症状はさまざまですが、試作基板だけではなく、量産基板でも起こっているので、深刻な状況になっています。お客様の手元に不良基板が山積みになっていることもありました。

試作基板における7つのトラブル例

BGA部品を使っている基板といっても、製品の用途・性能はさまざまです。今回は現場で起きている実装トラブルの例を3種類のサンプル基板でご紹介します。皆さんの基板はどのような構成でしょうか? また、これらのトラブルの経験はありませんか?

お客様から伺った「あるある話」と一緒にご紹介しましょう。

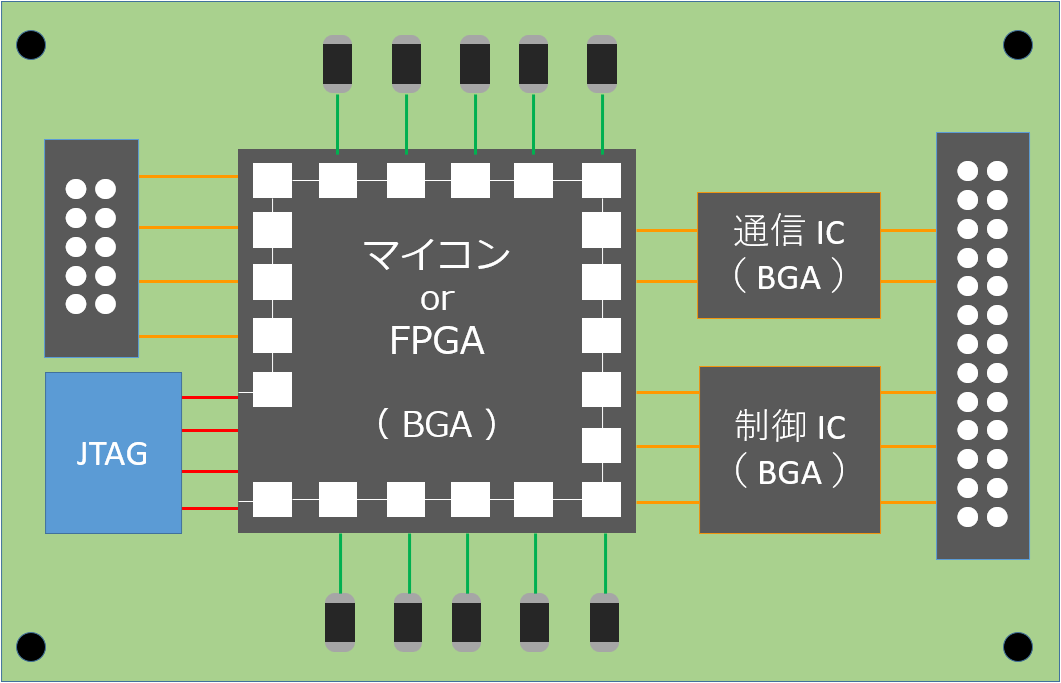

基板A : マイコン、またはFPGAを1つ使用した構成(組込み機器の通信、制御基板)

最初の基板は、小型の組込み機器の例です。1つの制御用マイコン、もしくはFPGAから通信用IC、制御用ICをコントロールする回路構成で、コネクタから外部に接続された機器と通信し、センサやモータなどを制御する基板です。

この基板で起こる可能性があるトラブルは2つあります。

しかし、状況は変わらず、プルアップ抵抗が外れていた。

仕方がないので、部品を交換してみた。

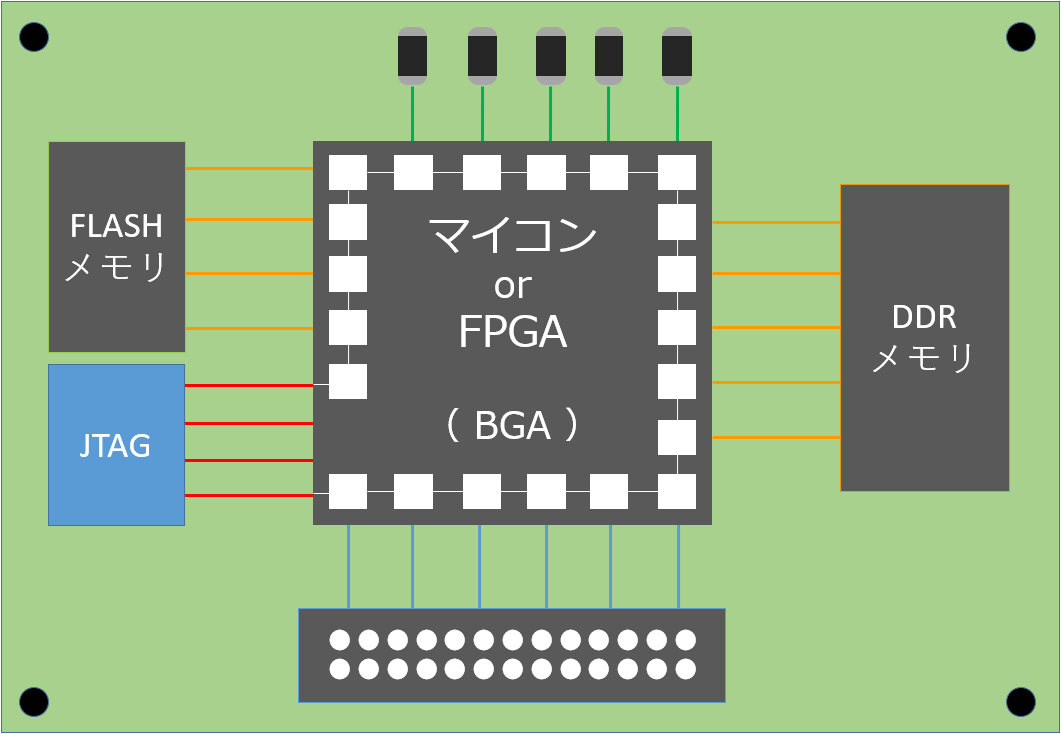

基板B : プロセッサ、FPGAとDDRメモリを使用した構成(画像機器、映像機器の基板)

次の基板は、画像処理、映像処理用の機器の例です。制御用のマイコンもしくはFPGAと画像処理用のDDRメモリが接続された構成で、プログラム格納用のフラッシュメモリが搭載された基板です。

この基板で起こる可能性があるトラブルは、①と②に加えて、さらに2つあります。

いずれのトラブルもBGA部品間は内層で接続される場合が多く、測定器では信号を観測することができません。多くの方がカンを頼りに、部品を交換しているのではないでしょうか。カンが当たれば修理成功、外れたら違う部品を交換されているようです。

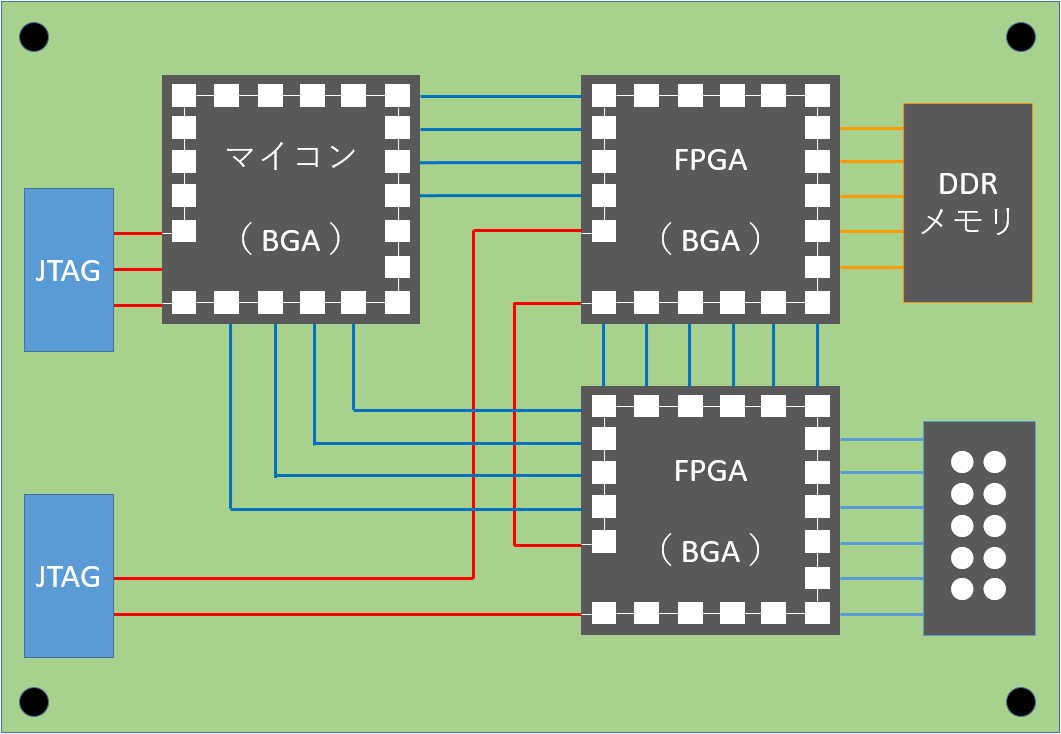

基板C : 大規模プロセッサ、FPGAを複数使用した構成(産業機器の基板)

最後は、産業機器などでみられる大規模な基板の例です。高性能のArmプロセッサと大規模なFPGAが多数搭載されています。FPGAは高価なもので数十万円するものもあります。

この基板では、これまで紹介した①~④のトラブルに加え、さらに3つのトラブルが起こる可能性があります。高機能なArmプロセッサ、大規模なFPGAは高価ですので、何とかして修理したいと考えますが、さまざまな条件が重なるため難易度は非常に高くなります。

FPGAでテスト用のロジックを作って測定できるようにしたが、デバッグのための開発に時間がかかった。

製造上の不具合を見つけるのに1か月かかった・・・

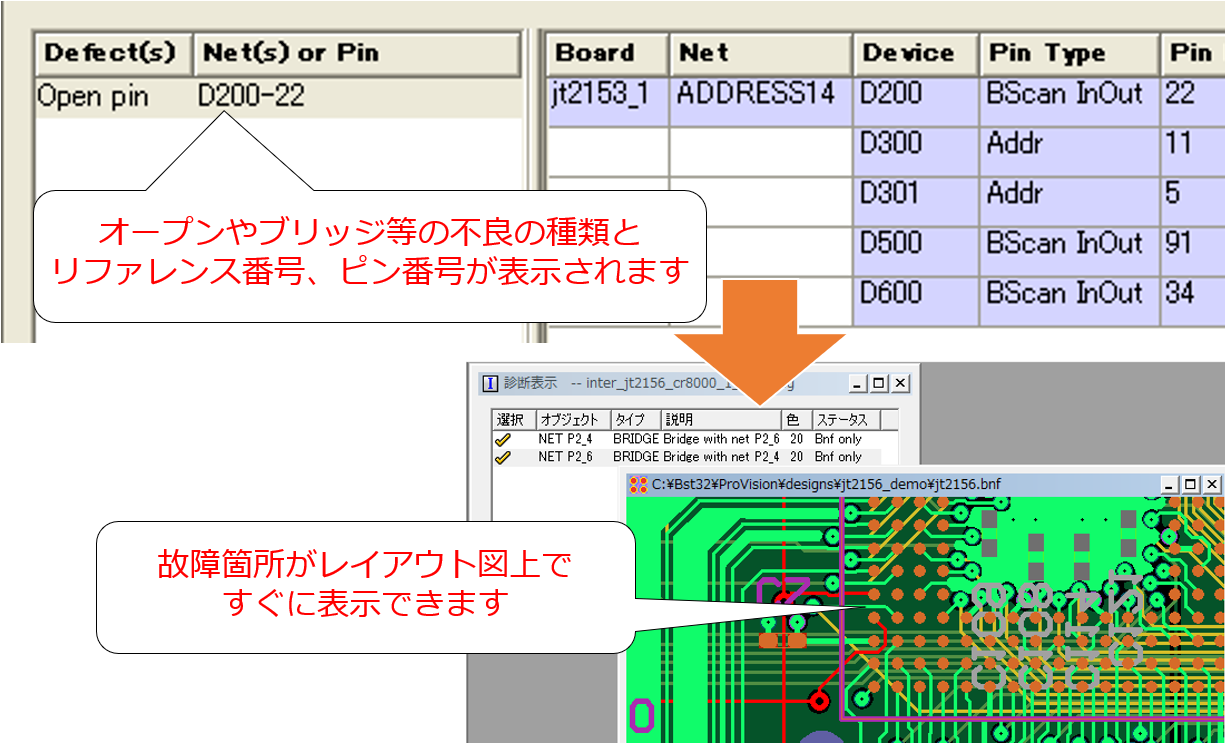

これらの7つのトラブルは、BGAパッケージの部品があると、どこに不良があるのかを見た目で診断することはできません。測定器で波形を観測しようと思っても、BGA部品のピンは触ることができませんし、高速伝送路にはテストパッドを配置することができないため、測定器ではプロービングすることができません。

そのため、対処方法としては「カンを頼りにして、手当たり次第に部品を交換する」ことが多いようです。また、モノづくりを確認するために、製品プログラムとは別にソフトウェアを開発したり、テスト用のFPGAのロジックを開発したりするケースもあります。

デバッグ作業で最も時間を費やしてしまうのは、「設計ミス」と「モノづくりの不良」が混在するケースです。ある機能が動かなかった場合に、多くの設計者は、モノづくりには問題がないと想定した上で、あらゆる設計要素を疑いデバッグを行っています。設計要素には、回路設計、基板設計、FPGAのロジック設計、ソフトウェア設計などがありますが、問題点を切り分けるための検証作業には膨大な時間がかかってしまいます。あらゆる設計上の問題がないと判断した上で、製造上の不具合が見つかるまで、デバッグ開始から1か月ほどかかってしまったという話を聞いたことがあります。これでは、新製品を開発するための貴重なリソースを無駄にしてしまいますし、新製品をリリースする時期も遅れてしまいます。

3つの基板の共通点は?

さて、今回ご紹介した3つのサンプル基板で共通している点にお気づきでしょうか? 答えは「JTAGコネクタがあること」です。FPGAのダウンロードやマイコンのソフトウェアデバッグ、プログラムの書き込み用に使っているという読者もいらっしゃるのではないでしょうか?

実は、本当のJTAGの使い方を知っていれば、この製造上の不具合と設計上の不具合を切り分けて、デバッグのムダを解決できてしまうのです。もともと、JTAGとは「Joint Test Action Group」という実装テスト用のアーキテクチャを考案したワーキンググループの名称です。このグループが中心となり、「JTAGバウンダリスキャンテスト」というBGAパッケージの実装テスト手法をIEEE1149.1として規格化しました。

日本では「JTAGテスト」と呼ばれています。JTAGテストを使うと、下図のようにBGAの実装不良箇所を自動診断することができるのです。

次回予告 「BGAのはんだ不良を見つける:本当のJTAGを知っていますか?」

今回は試作基板の開発現場で起こっているBGA実装不良と、デバッグ時のトラブル例を中心にご紹介しました。次回は、JTAGコネクタを使うだけで、試作基板のデバッグ効率を改善できる「JTAGテストのアーキテクチャの基礎」について解説します。皆さんが知らなかった「本当のJTAG」の姿が見えてくるはずです。

第1回 試作基板のBGA部品が動かない!?第2回 BGAのはんだ不良を見つける。本来のJTAGとは?

第3回 試作基板のデバッグで困らない。テスト容易化設計の5つのポイント

第4回 テスト範囲を最大化する「DFTサイクル」とは

第5回 テストパッド削減とデバッグに役立つJTAGテストの活用事例

第6回 BGA実装基板の検査の課題を解決したJTAGテストの活用事例

第7回 「JTAGテストとHALTを活用した品質保証の取り組み」

第8回 実態調査から見える実装基板のトレンドと検査の課題

第9回 デバッグとテストの課題を解決する検査手法

第10回 JTAGハイブリッド検査の最新動向

第11回 Pythonで動かすJTAGテスト

|

執筆者プロフィール 谷口 正純(たにぐち まさずみ) アンドールシステムサポート株式会社 入社後、組込み機器、産業機器の回路設計を担当。現在は、JTAGテストツール、自動テスト用のスイッチ&センサエミュレーションのマネージャとして、お客様の基板テストの改善活動を支援している。 また、エレクトロニクス実装学会において、検査技術委員会の副委員長、バウンダリスキャン研究会の幹事として、JTAGテスト技術を通じて日本のモノづくりの改善活動を推進している。 |