かゆいところに手が届く! 選りすぐり「Design Force 2019 新機能紹介」 第1回目:「時短編」

2019年04月23日2019年3月にリリースされた Design Force 2019 では、部品配置・配線・面などの設計をより一層効率よく行えるよう、さまざまな機能を進化させ、機能追加も行っています。

今号から3回の予定で、選りすぐりの機能を、実際操作した使用感も交えてご紹介します。

第1回目は「時短編」です。

5G時代に備えあり!『シールド発生機能強化』

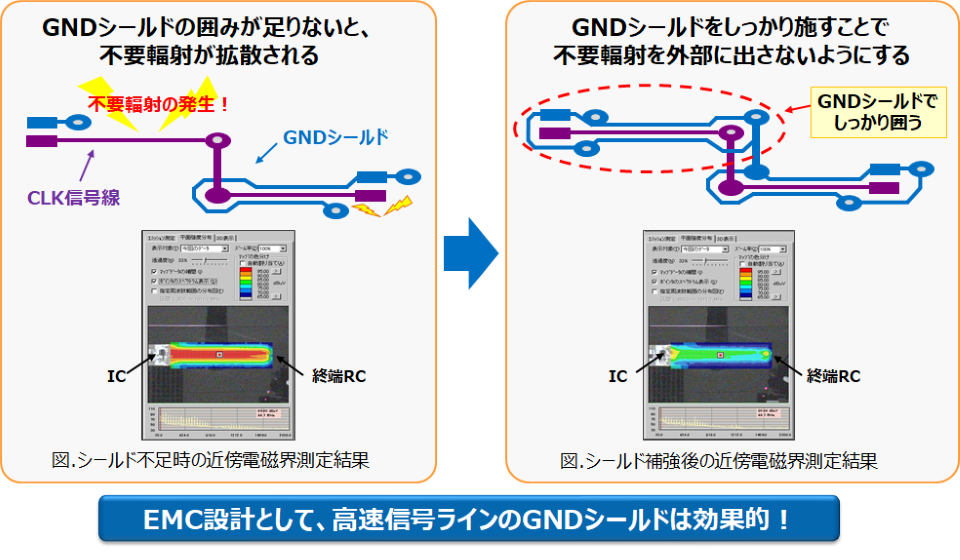

放射ノイズの出やすいクロックなどの配線は、極力GNDで囲む(シールドする)ことは、基板設計に従事する読者のみなさまは、おそらく実践されていると思います。

通常は図1のようにシールドパターンで囲い、ビアで内層グランド面に接続しGNDシールドします。

図1.GNDシールドによる効果?

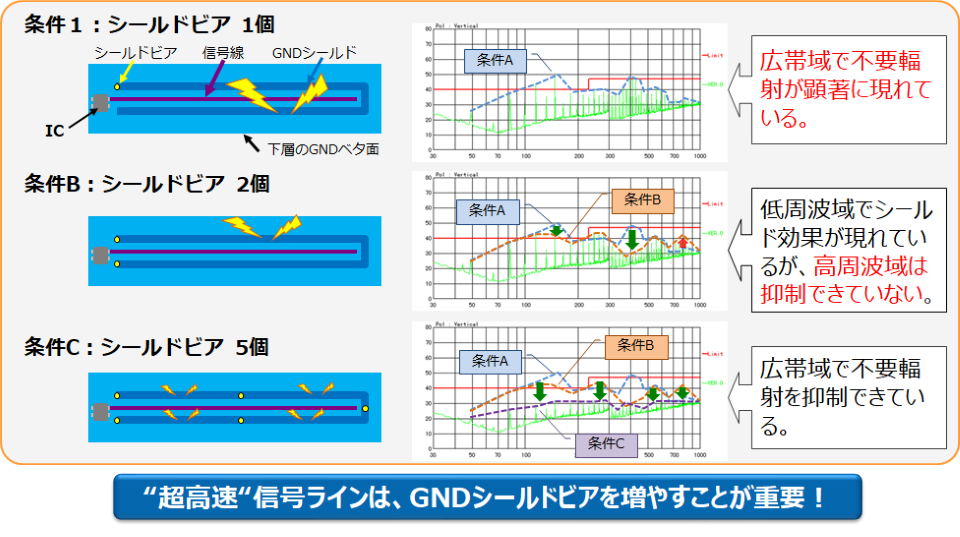

しかし、近年、通信のGbit化や、CPU、ASIC、FPGAなどで処理の高速化が進むのにともなって、GNDシールドをしていても不要輻射を抑えきれないという問題が深刻化しています。さらなる GND強化を目的として、ビア本数を増やす設計も増えてきています。

シールドビアの個数を増やすと、図2のようにEMCに効果があります。

図2.シールドビア個数による効果

しかし、ビアを打つのは手作業で、多くの時間を掛けられていると思います。

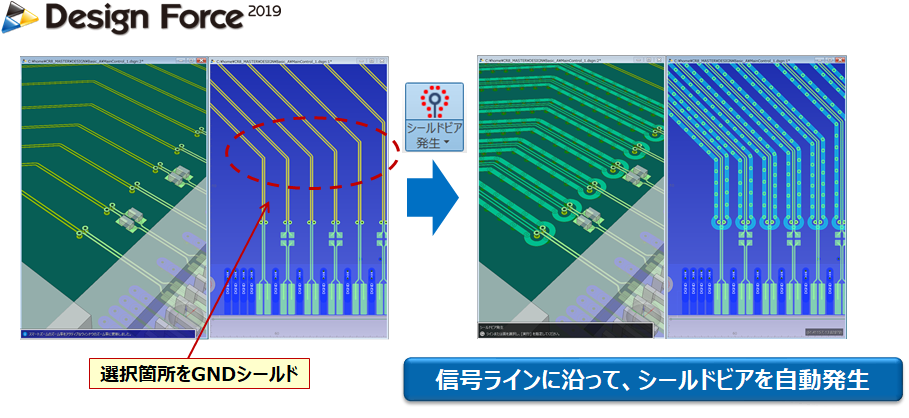

Design Force 2019 では、信号ラインの周囲にGNDシールドを自動発生する機能が追加され、煩わしいシールド配線およびビア打ち作業が大幅に時短できるようになりました!

図3.シールドビア発生

◆ここがイチオシ!

「シールドビア発生」機能は、パラメータダイアログを使って、ビアの間隔の調整や、GND面の付加が行えます。

確定前にイメージを見ながらパラメータを調整できるので、適切なGNDビアをすばやく作成できます。

イメージムービーをご覧ください。

他基板の配置・配線を簡単に流用!『基板間テンプレート配置・配線』

Design Force 2019 では、テンプレート配置・配線が進化しました。

「あの時、あの製品で配置・配線設計した、あのブロックを、今回の設計で流用したい!」 と思うことも多いのではないでしょうか。

これまでのCADでは、配置・配線の流用は、操作が複雑で難しい!と感じていた方も多くいらっしゃると思います。(以前の Design Force ユーザ事例紹介でキョウデン様からもご要望いただいていました。)

今回の Design Force 2019 では、ユーザのご要望に対応し、基板間で部品配置や周辺パターンを簡単に流用できるようになりました。

流用範囲の指定と取り込みだけのシンプルな操作で、ブロックの設計を大幅に時短できます!!

◆ここがイチオシ!

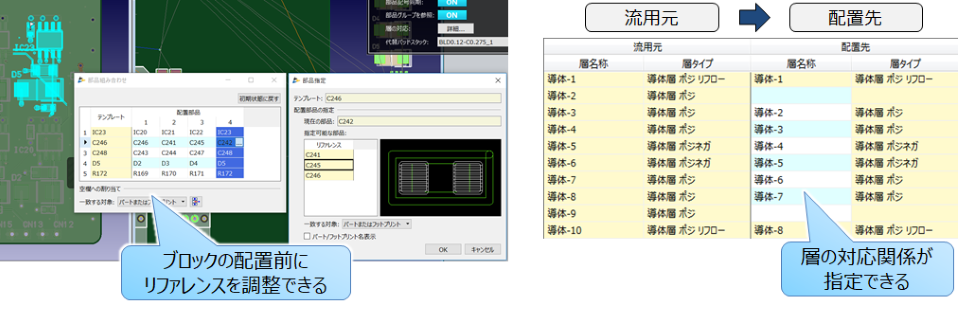

「基板間テンプレート配置」機能は、同様の配置・配線ブロックが複数ある場合や、流用先で基板層数が異なる場合でも、調整ウィンドウにて正確な操作が行えます。

候補となる部品を選択式で操作できるので、直感的で簡単に作業を行えます。

図4.流用先で部品配置のリファレンスを調整

それでは、一連の流れをムービーでご覧ください。

いかがでしたでしょうか。

今回、ご紹介した機能の他にも、まだまだ便利な機能がたくさんあります。

月例で開催中の「エクスペリエンス」で操作を体験していただけますので、ご興味のある方は、お気軽にご参加ください。参加方法は、リンクURLにてご紹介中です。

Design Force Experience 2019年5月

以上。次回につづく。