IoTの普及で電子機器設計の複雑化が進む

2016年05月25日IoT製品に求められる複雑な設計課題を図研のソリューションを使っていかに解決するかをご紹介している本記事。前回は、PCBと筐体、電子機器設計と機構設計との協調設計についてお話ししました。今回はそれに加え、システムレベルでの統合設計環境とIoTの普及にともない増加するアナログ回路との協調設計の必要性についてお話します。

ゴールドマン・サックスによれば、2020年までに腕時計から工場内設備にいたるまでの280億個のデバイスがモノのインターネット(IoT)に接続されると見込まれています。

前回は、ウェアラブル機器を例に、設計の初期段階で、クリティカルな設計要件を検討し、PCBと筐体を統合しながら設計することの重要性について説明しました。これは、一部の先端的な電子機器だけでなく、大量生産の電子機器全般に当てはまるトレンドだと考えられます。

今回の記事では、PCBと筐体、電子機器設計と機構設計との協調設計だけでなく、システムレベルでの統合設計環境、IoTの普及にともない増加するアナログ回路との協調設計についてお話します。

システム全体を考慮する協調設計の必要性

協調設計は、PCB設計と筐体設計との間で行うだけでなく、システム全体、チップ・パッケージ・PCBを含めて行う必要があります。

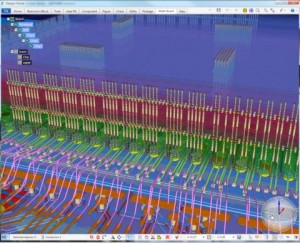

例えば、今まではチップ・パッケージ・PCBは、それぞれ独立した二次元環境で設計されていました。しかし、IoT(Internet of Things)やウェアラブル機器など最先端の機器では、機能が増えるだけでなく、短納期が求められ、コストの制約が厳しくなっている一方で、筐体はますます小型化が求められています。これらの課題に対応するには、電子部品のピン配列を最適化し、サブストレート基板の層数を最小化するなど、チップ・パッケージ・PCBそして筐体を含めて、それぞれが連携を取りながら協調して設計を行う必要があります。

システム全体の設計目標は、チップ・パッケージ・PCBという階層構造の中で、最短経路、かつ最小基板層数でチップ間の信号が接続できることです。これを行うには、これらの設計を統合した設計環境が必要となります。

設計環境を統合することによって、次のようなメリットがあります。

・チップ・パッケージ・PCBを同時に参照できるため、ピン配列をより早くより正確に最適化できる

・同一環境で、ICのRDL(再配線層)での配線、ダイ・バンプの配置、電源のメッシュプレーンを設計しながら、パッケージ、PCB、インターポーザを設計できる

・RDL(再配線層)での配線、IC側のピン配列、PCB側での配線引出しを考慮しながら、パッケージ層を最適化できる

図研のCR-8000 Design Forceは、チップ・パッケージ・PCBの設計環境を統合したシステムレベル・マルチボード設計環境です。パッケージ間で複雑に繋がれている信号も同一環境で設計、確認することができます。

アナログ回路の重要性が高まる

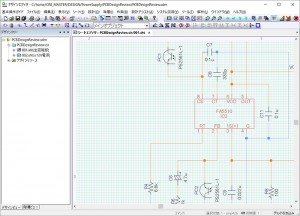

IoTの普及に伴い、多くの工場内設備が相互に接続され制御されようとしています。個々の設備の稼働状況や品質情報を上流の設備へフィードバック(FB)したり、逆に下流の設備へフィードフォワード(FF)したり相互に通信し、プロセス全体の運用効率を高めることが実現できつつあります。ここで重要性を増すのが、センサー、信号処理、ワイヤレス通信、電源のパワーマネージメントといったアナログ回路です。膨大なIoTデバイスにはさまざまなセンサーが組み込まれ、画像、光沢、色調、温度、物質成分などの情報を感知・測定し、デジタル信号へと処理され通信されます。

CR-8000では、デジタル回路のみならずアナログ回路の設計のための豊富な設計機能をもち、上記のようなデジタル回路とアナログ回路が混在するPCBの設計において強みを発揮します。複数のエンジニアがデジタル回路とアナログ回路のエリアをPCB上で分割し相互に協調しながら設計を進めることができます。また、アナログ回路はキーデバイスを中心に、周辺回路も含めた回路ブロックならびにPCBレイアウトブロックとして容易に再利用できます。

協調設計環境における解析

それでは、競争力を高めリスク軽減を担保するための協調設計における解析へのアプローチはどのようにすればよいのでしょうか。システム全体での解析においては以下のようなことが重要です。

・オープンアクセスによるデータベース定義、あるいはGDS、LEF/DEFといった規格フォーマットを介した複数ICのデータ取込み

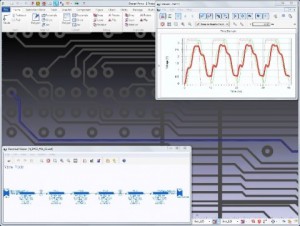

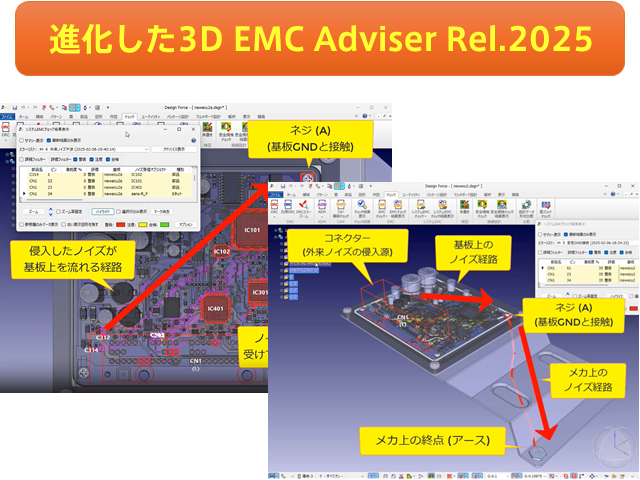

・SI解析、PI解析、電磁解析、高周波(RF)解析といった複数物理領域の解析を統合した設計・解析環境(図3を参照)

・登録コンテンツが管理されている回路ブロック、部品表、レイアウトブロックを再利用できる再利用設計環境

・マルチボードを三次元設計できる環境

CR-8000 Design Forceは、チップ・パッケージ・PCB設計の階層全体の最適化を実現するための協調設計環境なので、設計対象物の性能を高めつつ、製造コストを低減することもできる設計システムです。エンジニアはシステムレベルの視点で、機能、価格、性能、サイズ、重量および外形デザインの各要素間のトレードオフを常に考慮しながら設計を進めることができます。

0

製造業のIoT化に伴うセンシングや多種大量データ処理、ワイヤレス通信などは、今後、様々な電子機器においても重要な技術となってきており、デジタルとアナログの混在に対応したPCB設計環境が必要となります。また、複雑化・短納期化などさまざまな課題を持つ製品開発においては、PCBのみならずシステム全体を俯瞰しながら設計できる統合設計環境が課題解決の近道となるでしょう。

Humair Mandavia

Humair Mandavia

こんにちは。図研創造センター(Zuken SOZO Center)のエグゼクティブディレクターを務めるフメア・マンダビアです。創造センターはシリコンバレーに2013年に新しく設立されたR&D拠点です。私のキャリアは、通信業界におけるハードウェア設計者から始まり、2004年にZukenに入社し、アプリケーション・エンジニアとして働くようになりました。テキサス大学ダラス校で、電子工学の学位と経営修士(MBA)を修得しています。休日は二人の子供と自宅で過ごし、たまに友人たちとゴルフ、バスケットボール、自転車を楽しんでいます。

これからも、シリコンバレーから最新の技術情報を発信していきますので、よろしくお願いします。