コストとパフォーマンスを最適化する三次元協調設計環境

2016年01月21日Zuken SOZO Center Humair Mandavia

Club-Z読者の皆さまこんにちは!アメリカシリコンバレーにあるZuken SOZO Centerのフメアです。

私のいるシリコンバレーでは、皆さんも御存知の通り、沢山のイノベーティブな企業が先進的な新製品開発に取組んでいます。そんな企業の開発者の方々に、今大変興味を持っていただけるテーマが「半導体、パッケージ、PCBのco-design(協調設計)」です。

私のいるシリコンバレーでは、皆さんも御存知の通り、沢山のイノベーティブな企業が先進的な新製品開発に取組んでいます。そんな企業の開発者の方々に、今大変興味を持っていただけるテーマが「半導体、パッケージ、PCBのco-design(協調設計)」です。

次々にリリースされる高性能の最新半導体のパフォーマンスを使って出来る限り早く、しかも低コストでユニークな新製品に具体化していくためには、この技術が非常に重要になっているからです。

図研のソリューションを使ってどのようにこれからのco-design環境を構築できるかについてホワイトペーパーを書きましたので、Club-Z読者の皆さまも是非御覧下さい。

今後も、時々こうした技術情報をお送りしていきたいと思います。ご意見ご感想などお聞かせいただければ嬉しいです。

要約

1個の半導体に複数の機能を実装するSoC(System on Chip)は、パッケージ上に複数チップを実装する技術と組み合わさることによりパッケージ、プリント基板(PCB)と集積回路(IC)を跨いだ最適化設計に新たな課題をもたらしています。一般的に、チップ、パッケージ、基板は、3種類の独立したツールで設計されます。それらのツール間では連携が取られていないため、他のツールの設計データを活用するには連携用のデータを加工・生成する必要があります。

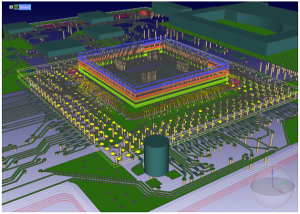

今回紹介する三次元協調設計環境は、IC、パッケージ、基板設計を統合し、かつ三次元での検証が行える設計環境です。この環境があればチップとパッケージ、基板を考慮しながら層数を最小限に抑えるためのピン割付の最適化や配線作業の容易化が行え、より高いパフォーマンスとより安価な製造コストを得られます。

パッケージデザインの課題

高性能なICを設計するには、的確なパッケージング技術とPCB上の実装戦略が不可欠です。 今日のIC設計、特にアプリケーション・プロセッサは、大半のモバイル製品の中で最も重要な構成要素であり、電気、PI(Power Integrity)、SI(Signal Integrity)、機械的および熱的要件を満たすために、より洗練されたパッケージング・ソリューションが求められています。トランジスタを縮小するコストメリットが少なくなり、半導体メーカ各社はメモリとプロセッサを統合する様々な技術を開発してきました。シリコンのコスト増加分を補填するために、ICとICを近接して実装するための新たなパッケージの登場もそのうちの一つです。

PoP(Package on Package)構造は、短い配線でロジックICとRAM(Random Access Memory)を接続することができ、スマートフォンやタブレットなどに広く使われています。また、SiP(System in Package)のような高密度実装技術は、ミックスド・デジタルやRF(高周波)アプリケーションにおいて、複数チップをパッケージに搭載するために利用されています。

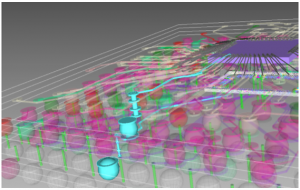

三次元IC技術では、ボンディング・ワイヤを用いずに図2のようにTSV(Through-Silicon Via)を用いて配線することにより積層型チップ間の相互接続距離を短くすることができ、高速性能と低消費電力を実現しました。

パッケージ・モジュールの多機能化により、ますます複雑化するパッケージング・ソリューションは、パッケージ設計者だけでなくパッケージを実装するICやPCBの設計者にも、多くの課題を与えています。

従来のシステム設計では、IC、パッケージ、PCB設計それぞれスタンドアロンで動作するツールに依存していました。このような環境はシステム・レベルのプランニングや、可視化、設計や解析をするのには不向きです。プランニング中の設計データと、レビュー・解析時のデータとで相互に連携が取れないため、プランニングの指示内容が最終製品に反映されたかを確認するのは大変です。また、設計ツールが独立しているため設計者は各自の設計範囲しか見えず、さらにツール間でのデータ交換用ファイルフォーマットも統一されてないため、他のレベルとの協調設計も難しい状態です。システム全体を統合し、かつ電気的、機械的情報の両方をサポートした協調設計を実現できるツールが存在しないのが現状です。

このような状況でも、サーバや産業機器のような複雑なシステムであれば、装置全体からみたパッケージやサブストレートのコストが僅かであるため設計はできました。しかし、今日の自動車やウェアラブル製品のように多機能化した製品では、より厳しいコストの制約が求められ、製品サイズの小型化にともない、基板層数も少なくする必要や部品のピン割付を最適化する必要が生じるため、システム全体での協調設計は不可欠です。

ツールが連携されていない環境では、プランニングや実現可能性を検討するために、スプレッドシートや一般的なオフィス製品を利用してツール間のデータ変換を定義しています。変換のためのファイルは各企業内で開発、メンテナンスされており、設計ツールとは別に手動で操作する必要があります。このような環境では、プランニングデータと最終的な設計データとが自動的に整合性が取られることはありません。部品のピン、入出力、配置配線の最適化を行うにはシステム全体での検討が必要であるにもかかわらず、現状の手動での連携、フィードバックの方法では実現が難しい状況です。

この状況を受けてPCB設計ツールベンダーは、これらの課題に対処したツールを提供し始めています。しかし、それらは従来の製品をベースに開発されているため、二次元環境の制限を受けたり、柔軟性に欠けたりするため、単一のパッケージと単一のPCB設計という範囲にとどまっています。また、二次元と三次元を切り替えて確認するには、従来の二次元データを三次元ビュアーデータに変換する必要があるため、手間とデータ表現の正確性にも問題があります。

製品の外形寸法の小型化により、機構設計で設計した筐体と電気設計上のフットプリントをチェックし、筐体を考慮した物理的な解析へのニーズも高まっています。筺体が複雑な形状になるにつれ、二次元ビュワーでは正確な表現が難しくなり、三次元ビュワーが求められています。従来の設計フローでは、電気設計と機構設計相互に跨った解析をあまり必要としなかったため、それぞれ設計が分断されていました。しかし、システム全体を統合して検討するには、固有のテクノロジ・ファイルで定義されるサブスレート基板を制限なくサポートし、正確な機構設計データを基板設計に活用できる環境が必要です。製品が複雑化するに伴い、三次元設計で正確にビジュアル化できることが求められます。

システム・レベルの3D協調設計の登場

三次元協調設計環境によって、プランニングと最終設計物を統合できる新たな時代に突入します。

統一されたビュー、統一されたUI(User Interface)で、システム・レベルの設計、IC設計、パッケージ設計、PCB設計の全てが行えます。

これにより筐体設計では、最終的な電気設計データ上のPCB、パッケージ、ICの外形寸法使った嵌合とクリアランスの確認ができます。また、製造容易性設計(DFM)機能も用意されているため、レイアウト設計中に組立、実装に関する製造性チェックが行え、サインオフと製造のためのドキュメントも自動的に作成できます。さらに、1クリックでマルチ・フィジックス解析(電気、熱、応力等複数の物理領域の解析)も実現できます。

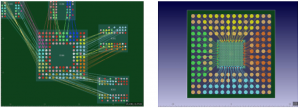

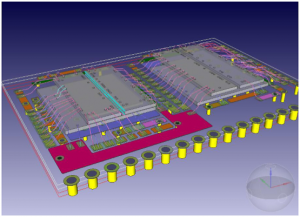

このように統合された協調設計環境であれば、いままでの二次元ツールでは実現できなかった設計が行えます。例えば、一つのデザインビューを介して、IC側の再配線層(RDL:Re-Distribution Layer)での配線とPCB側の配線引き出しを確認しながら、パッケージの配線層数を事前に検討できます。(図3参照)

チップとパッケージのシステム・レベルでの協調設計が行えるようになると、PoP、SiP、チップスケールパッケージや三次元ICパッケージのような垂直方向に配線する複雑な構造でも、システム全体を考慮してバンプとボールの配置、ピン割付の最適化が行え、チップ、パッケージ、PCBの層数を減らすことができます。

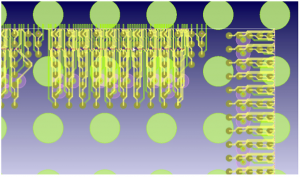

チップの再配線(RDL)とパッケージの配線引き出しは自動で行われ、バンプの配置を最適化できます。これにより、信号のパフォーマンスを向上させ、再配線層(RDL)、インターポーザ、サブストレート、パッケージの層数を短期間で減らすことができます。

図4のように、一つの設計ビューで同時にIC、パッケージ、PCBを表示できるため、ピン割付の最適化と接続エラーの回避が即時にできます。パッケージとICのバンプを割当る際には、PCBレベルでのラッツネストを踏まえた検討が行えます。さらにPCB上の配線容易性を向上させるためのピン交換が必要となった際には、パッケージやICレベルでの影響も確認できます。

ピン交換を行うと、パッケージとPCBのデータベース間で自動的に通信が行われるので、CSVファイルや中間フォーマットを介した連携は不要です。複数の設計者が同一のサブストレートを設計する場合には、他の設計者の編集作業を保護した状態で作業ができ、またロックされたパッケージのピンを交換したい時には、ツールから他の設計者に設計変更(ECO)を求めることができます。

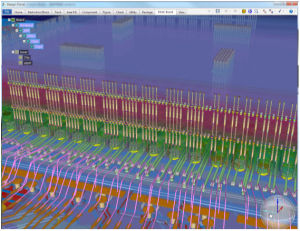

三次元協調設計環境では複数のICを協調設計環境に取込み、相互に接続することが可能なので、図5にようにPoPやSiPのような複雑なパッケージ間の配線をより高度に管理できます。リアルタイムな三次元設計機能によって、SiPに着目したデザイン・ルールチェックや、ボンディング・ワイヤが任意の角度で間隙を満たしているか、ワイヤの断面が製造仕様を満たしているかなどを細かく確認できます。

三次元協調設計環境には、チップとシリコン・インタポーザを積層した三次元ICのようなTSVを使用した設計における有用な機能も用意されています。例えば、既存のデータベース(OpenAccess、GDS、あるいはLEF/DEFファイル)から設計情報を取り込み、TSVを発生させることができます。TSVは、製造ルールと設計ルールを元に、自動配置、自動配線が行え、設計者は複雑な配線引き出しと配線構造を三次元で確認できます。

RF部品をモジュールに組み込む際、狭いスペースにより多くの機能を詰め込むには、ダイや積層したダイを埋め込み型の配置へと変更する必要があります。三次元協調設計環境では、即時に代替のキャビティ構造を評価でき、PCBサイズを最小化するための空間検討が行えます。 (図6)

例えば、RFモジュールの外形サイズ6×8mmを4.5×6mmサイズに縮小するとします。サブストレートが小さくなった場合、ワイヤボンド接続のチップでは対応できないため、フリップ・チップに置き換えてボードの内層に埋め込みます。RFチップの再配線層の配線は、モジュールとPCBに対して最適化した状態で行われます。また、三次元表示により新しいRFモジュールは新しい外形仕様に合っていることが確認できます。

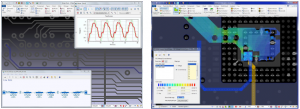

システム全体のどのレベルで変更が発生しても、設計者はSI、PI、熱の観点での影響を確認できます。(図7)

キーサイト・テクノロジズ社、ANSYS社、ナショナル・インスツルメンツ社、CST社、シノプシス社のようなソリューション・プロバイダのソリューションを用いて、マルチ・ディスィプリン(複数分野)、マルチ・フィジック(複数の物理領域)解析を実行できます。

協調設計環境では、システム全体に渡った信号のトレーサビリティを確保できます。システムの相互接続を介してドライバからレシーバまで設計と部品の境界を横断するように、信号経路をレビューや解析できます。

PCB設計では、筐体形状を直接レイアウト形状に取り込むことができ、筐体形状を考慮したPCB設計が行えます。初期設計の段階から筐体内にPCBを配置することで、リアルタイムに最適化、干渉を考慮しながらレイアウト設計ができます。

下請企業やパートナ企業に設計をアウトソースする場合、外部に出る設計情報は極力減らす必要があります。通常は、設計やエレキCADの詳細を把握しているスキルの高いエンジニアが、設計情報の加工に多くの時間を費やし設計データを準備することになります。しかし、この協調設計環境では、設計情報のパーミッション・コントロールをメニューから細かく定義できるため、設計IPの安全性を容易に確保できます。

まとめ

三次元協調設計環境では、チップ、パッケージ、ボードの設計全体を統合したシステム・レベルでの協調設計により、設計コストは削減しつつ、製品パフォーマンスを向上できます。三次元協調設計環境を使うと、チップ、パッケージ、ボードの設計環境間の手動でのデータ変換は不要となり、複雑なデータ構造でも、三次元表示により設計上のトレードオフの効果を把握でき、個別の設計を行いながらシステム全体の検討課題を考慮できます。

また、マルチ・フィジック解析ツールとの密な連携によって、コストとパフォーマンスの最適なトレードオフが行え、システム設計上の問題をプランニングすることや、その問題に対して素早いフィードバックが行えます。

加えて、設計環境が独自に用意したデザイン・ルールによって、顧客固有のルールを生成するために投資することなく設計品質を高められます。

このチップ・パッケージ・ボードの三次元協調設計環境を用いることにより、設計者は将来の複雑なシステム設計に取り組むことができるようになります。(完)