後工程実装の盛り上がりと図研の3D-IC・チップレット設計への取り組み 第2回

2024年03月20日図研は、PCB設計ツールベンダーとして知られていますが、2000年代よりチップレットやアドバンスドパッケージ設計にも注力しています。従来のEDAツールは、シングルチップ/シングルパッケージ設計に特化していましたが、「CR-8000」は、2.5D/3D設計機能を備え、マルチチップ/マルチパッケージ設計を可能にしました。 シリコンバレーの主要半導体メーカーでの採用、他社に先駆けたダイ/インターポーザー/パッケージの一体設計実現などを経て、図研はこの分野の協調設計でのリーディングカンパニーとなっています。

(Club-Z編集局)

そういうわけで、シノプシスと連携しているんですね。

(仮屋CTO)

そうです。シノプシスがここまでやってくれれば、インターポーザーとパッケージ情報は両方扱えるので、後工程はわれわれがすべてできますよという話をしています。

他社EDAベンダーは2種類のデータベースが全然違うツールを出しているんですが、最近パッケージのCADツール上で階層構造としてモジュールを扱うものも出してきています。

こうして他社は必ず技術的領域でもキャッチアップしてくるんですが、かつてそうだったようにマスプロダクションからはみ出すニーズが必ず存在していて、そこでわれわれはお客様の要求を聞いて先手を打って動いていくので、必ず一歩先は進んでいけると思います。最終的にはもちろんマスプロダクションの世界まで行きたいんですが、やはり先端技術の世界で最先端を走り続けていたいというのが基本的な軸ですね。

あとは今回Rapidus様がいっているような、2nmまで積むようなチップレットの世界というのは実例がほとんどないので、そういう世界でやっぱりわれわれにしかできないことがあると思っています。

他社がつくる2種類のEDAツールを組み合わせた標準的な世界や、シノプシスがシリコン上でやる世界というのは当然そこはそこであると思うんですけど、それとオーガニックが混在するような世界とか、インターポーザーが一部シリコンだったり、一部オーガニックだったり、そこは両方できないですから。

また、シリコンブリッジとか、有機インターポーザーもそうですよね。圧倒的に有機インターポーザーの方が歩止まりは良いですけどね。結局こうして混在するはずなんですよね。

(仮屋CTO)

例えばチップレットは、いろいろなチップを組み合わせてつくっていくと思うんですね。そうすると、お客様もいろいろな会社とコラボレーションしなきゃいけない。

他社EDAベンダーは囲い込みというか、全部自社の中でやっていくんですが、図研はコラボレーションを大事にしているんですね。シノプシスとの協業はもちろんですけど、他のEDAベンダーとも共存しながらお客様に設計ソリューションを提案できるところが特長ですね。その方がお客様の自由度が高まると思います。

例えば、自社では他社ツールAを使っているけど、パートナーの会社は他社ツールBを使って、もう一社は他社ツールCを使ってバラバラなんだけれども、それを連携してやりたいという時に、われわれがハブとなって先程いったような、全体のシステムレベルのソリューションを提案できるのではないかと思います。

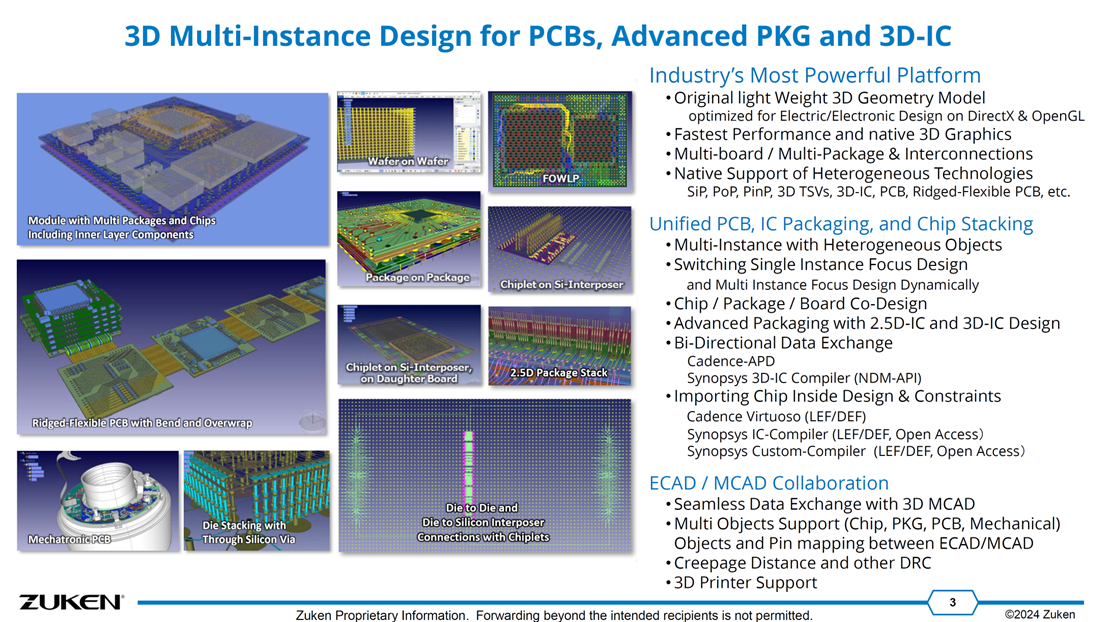

そもそもわれわれが今の技術をやるようになったのは半導体関連ではなくて、もともとはこういうリジッドフレキなんですよ。リジッドフレキって、実はチップレットでやろうとすることとものすごく構造が似ているんですよ。マルチインスタンスでヘテロジニアス※3なんです。フレキ層があって、フレキ層の表面と裏面から基板を貼り付けるじゃないですか。表面と裏面ってテクノロジーが違うんですよ。表面は2層板で裏面は5層板のビルドアップだったり。要はテクノロジーも精度も違うものを貼り付けるんですね。携帯電話も基板1枚に見えますけど、実際5~6枚はリジッドフレキやフレキで繋がってますよね。

1個1個にそれぞれ合わさるテクノロジーを集めるということです。

※3 異種混在のという意味で、ヘテロジニアスインテグレーションは種類の異なる複数の半導体チップ(ダイ)を1つのパッケージに収めること。

(Club-Z編集局)

リジッドフレキの表と裏は、そもそも製造プロセスとして違ったから、今のチップレットとほぼ同じということですね。

(仮屋CTO)

同じです。別々につくって貼り合わせるという意味では、CADのデータベース構造はほぼ同じですので、これをやったことによってわれわれはこの世界をほぼ何もしなくても実現できるようになったんですよ。

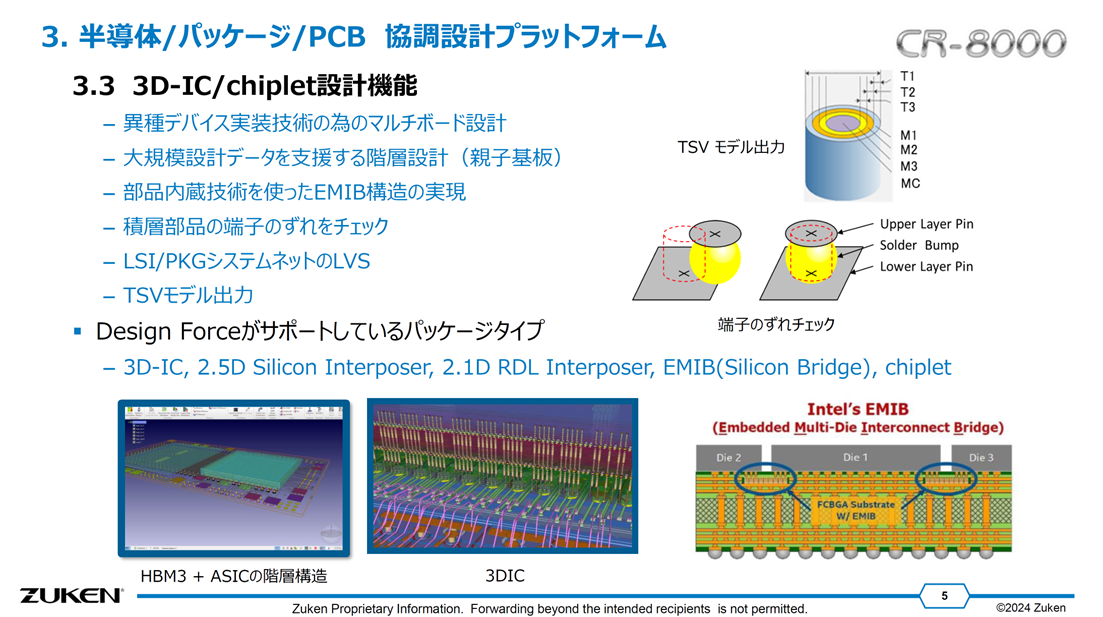

こちらのスライドの左上はパッケージスタックをしてチップを裸で乗せてワイヤーボンドで繋いでいる構造。こういう技術が図研のCADではさっき触れたようにデータベースの構造でできていたというのはあります。これもわれわれが先手を打ってやったというよりは、マスプロダクションではない世界のニーズを受けてやっていたらこうなったという経緯ですね。その一方で、結果的にこれらは今全部マスプロダクションになっています。

携帯電話ももちろんマスプロダクションですし、リジッドフレキも普通に量産される時代になってきて、チップレットもおそらく最初のうちは特殊目的で使われるでしょうけど、どこかで全部じゃないにせよ、半数近くはマスプロダクションでも使われるようになると思うんですよね。ただし今のままの歩留まりでは難しいかもしれません。

あとは結果的に、一社ではやはり難しいんじゃないかと思います。そもそもヘテロジニアスでかつテクノロジーの異なるチップを同じインターポーザーに実装するために、1社で2ナノも4ナノも、10ナノもつくるのは正直いって相当難しいんですよね。しかもそれをよそでつくって、一つの会社の中でだき合わせるのが難しい。

そうなると、やっぱりジョイントでつくるしかないと思うんですよ。実際、みんなそうなると思っているはずです。

かなり極端な話ですが、今回のSEMICON Japanに、Zero ASICっていう会社があったじゃないですか。面白かったですよ。インターネット上にチップレットが売っていて、それを選んで発注して要求資料を出すと、実装して送ってくるという。

そんなことできるわけないと思うんですけど、それで会社つくっちゃうくらいで、現実にはそういうことを考えている人たちもいるので、そういう時代が来るかもしれません。そうなってくると、複数の会社で関連して仕様をお互いに共有してインターポーザー上の仕様だけ決めて、その上のチップレットを別の会社でつくって、今パッケージ上にOSAT※4が実装しているように、OSATがインターポーザー上にチップレットを各社から集めて実装する時代が来るかもしれません。そうすると、マスプロダクション側でも使えるようになるんでしょうけど、そこまで行くにはいろんな特殊用途で技術を積んでいかなければならないと思います。

※4 Outsourced Semiconductor Assembly and Testの略で、半導体製造の後工程を請け負う企業。

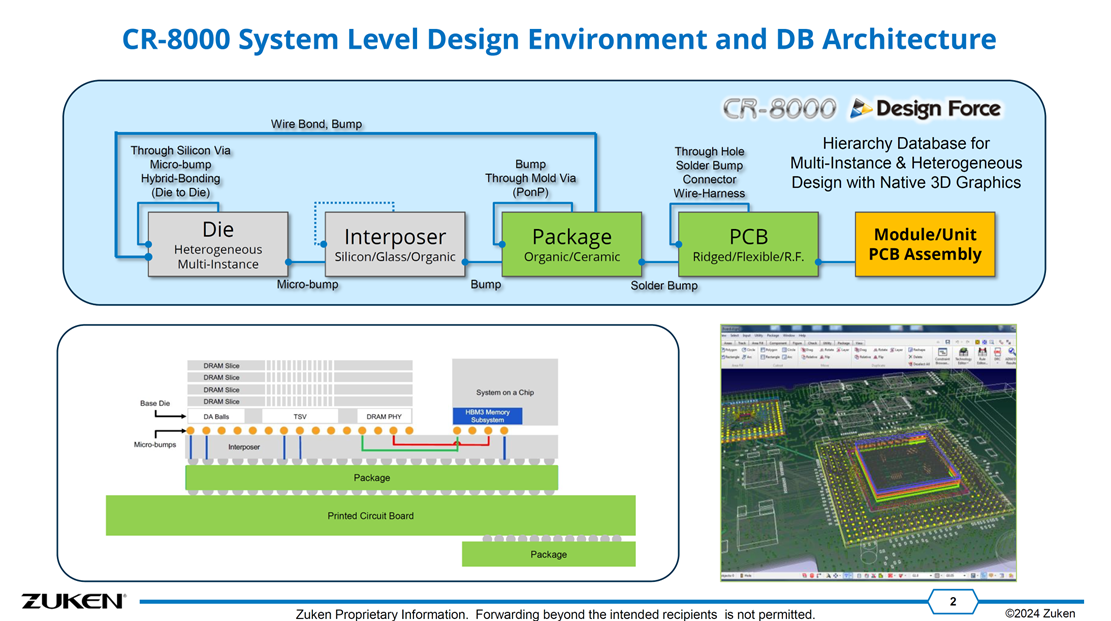

今日現在で、この黄色のモジュール・アセンブリから、PCB、パッケージ、インターポーザー、一番左のダイまで、全部データベースで持っているのは図研のCADしかないんですね。左3つ、右3つとか真ん中2つとかはあるんですけど、われわれはこれらを全部扱えますし、かつダイの中身は空っぽでも設計できるし、ダイの中身が出来上がってきたらダイの中身を読み込んで、ダイの中身の情報を抽出して解析することもできるんですよね。

(Club-Z編集局)

図研とシノプシスの連携の内容について詳しく教えてください。

(仮屋CTO)

これは左側にチップセントリックと書いてあるんですけど、半導体をつくる人たちが主流に設計するプロセスですよね。チップの仕様を決めてつくっていって、半導体自体をどう構成してつくるのがベストかというので、半導体をつくりやすい視点でモノをつくっていくプロセスで、これで出来上がった部品ってとても使いにくいんですよ。ピン位置とか熱の放熱とかを考えると、ものすごく使うのが難しかったりする。半導体ドリブンでつくっちゃうんですね。

今ソシオネクスト様みたいな会社は、それをシステムセントリックでつくっていて、使う側のニーズでこっち側にこの信号のピンを置いて、この電源系統はこっち側にまとめたいといったニーズを組み立てて渡すと、より使いやすい半導体ができますよね。

図研はシステムセントリック側でプランニングしてパッケージの並びを決め、ピンの配置を決めてその情報で最適化し、これだったらプリント基板上で作りやすいねとか、このサイズだったらこのサイズのパッケージに収まるし、マルチで乗っけてもこのインターポーザーサイズでOKだねなどと検討した上で、向こう側に渡してそれを連携、統合するということを進めています。

図研がシノプシスとやっているのは、チップセントリックのプロセスとシステムセントリックのプロセスを、お互いに流してここで繋いでしまえと、チップセントリックからシステムセントリックに渡すこともあれば、その逆もあるという。やり取りしながら、最適化するのがいいんじゃないかという話をしています。

(Club-Z編集局)

例えば、お客様からの要望としてはどういうアプローチが考えられますか。

(仮屋CTO)

われわれのお客様はシステムセントリック側から要望が来るわけなんですが、例えば自動車の中に電子制御ユニットを置きますよと。電子制御ユニットは熱源に近いので、温度はこのくらいまでありますよ。放熱容量はこのくらいですよ。ピン配置としてこっち側とこっち側にコネクターがあるので、半導体の位置はこうだよねとプリント基板上で決めながら、パッケージのピン配置はこっちがいいよね。だとすると、これは1個のパッケージにまとめて信号を出してもらった方が良いので1個のパッケージにしてよ、という情報を渡すと、それを受け取ってインターポーザーの分割をプランニングする、というようなことです。

分業ラインがどこにあるかによって柔軟に対応する範囲を決めて渡すという流れですね。

シノプシスの3D-IC Compilerと図研のDesign Forceをどこまで使うかという境界線をお互いに切り替えればいいし、ある領域はわれわれのツール間通信でオフィスが離れていても通信連動できるので、それと同じようにシノプシスのツールと一緒につくっていくというようなフローです。

例えばシノプシスを使っているシリコンバレーの半導体のエンジニアとパッケージ設計をする台湾のエンジニアが、ネットワークでつないで通信しながら最適化できる、そういうことを目指しませんか、という話を今シノプシスとやっています。

要はこの境界線はユーザーがどこまでやるかによって自由に変えられます。インターポーザーまで図研でやることもできますし、インターポーザーはシノプシスでやることもできます。

(Club-Z編集局)

面白いですね。シリコンバレーには上流の設計者しかほとんどいないでしょうから、そこにいる人が台湾とか日本のパッケージの人、もしくはPCBの人とせめぎ合いながら、同一ツール上で連携、分業していくという仕組みですね?

(仮屋CTO)

そうですね。

実は図研のCR-8000だけでも設計の分業ができていて、例えばプリント基板が全部で5枚あって、この4枚はあなたがつくって、この1枚は台湾でつくるからと。それを普通のネットワークを介して通信しながら連携してトータルの環境を見ながら設計できます。

図研は両方に共通の処理だけが反映されるという仕組みをもともと持っています。例えば、携帯の基板をつくる時にリジッドフレキに乗っかっている基板それぞれを、別々な人がつくれるような仕組みでないとどうにもならないわけですよ。片方の人がコネクターのピンを入れ替えたら、もう片方の人も入れ替えなければダメですよね。ですから、こちら側の人が入れ替えると、あちら側で入れ替えたことを知らせるエラーが出るみたいな仕組みがCAD上にあるんです。それをそのまま使えるので、これと同じことをシノプシスともやろう、という話を今しています。

(Club-Z編集局)

会社を横断してということですよね。

(仮屋CTO)

今はもう分業が前提ですので。ただし、分業しているからといってCADデータをお互いに開示して一つのデータをシェアするような設計を、台湾のOSATと日本の半導体メーカーがやるかどうかはまた別の話です。