【第2回】実装方式とパッケージの変化

2023年09月06日「こんにちは、鈴木です。星さん、先日は電子機器と基板の進化について教えていただき、ありがとうございました!今日も是非、基板について教えてください。」

「おっいいね、その打てば響く感じ。じゃあ、早速始めようか。

まず、鈴木君、プリント基板の実装方式とかって聞いたことある?」

「いいえ、聞いたことないです。是非一から教えてください!」

「OK!まず、プリント基板に電子部品を載せて、はんだで付けることを部品実装って言うんだけど、その方式は大きく分けて二つあるんだよね。

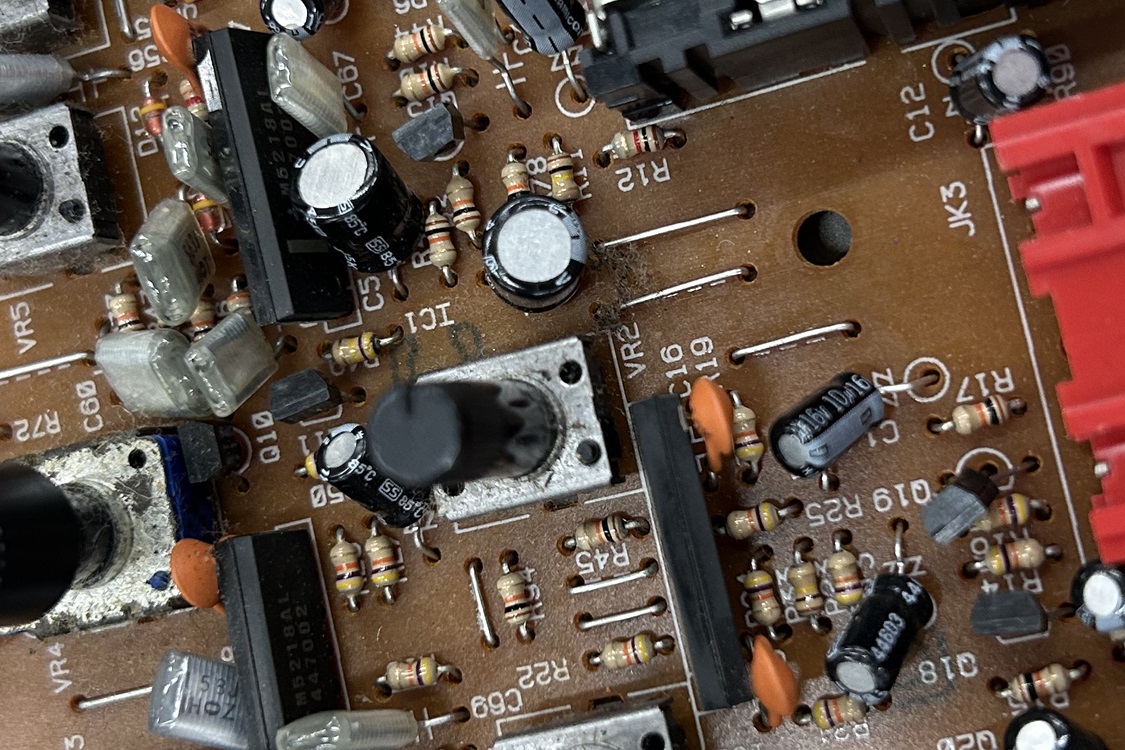

ひとつは、リード挿入実装方式といって、部品からリード線が出ていて、これをプリント基板のスルーホールという穴に挿入して、はんだ付けをするやり方なんだ。ただ、この場合基板を貫通する穴をあける必要があるから、配線とか部品を載せるスペースの邪魔になってしまうんだ。

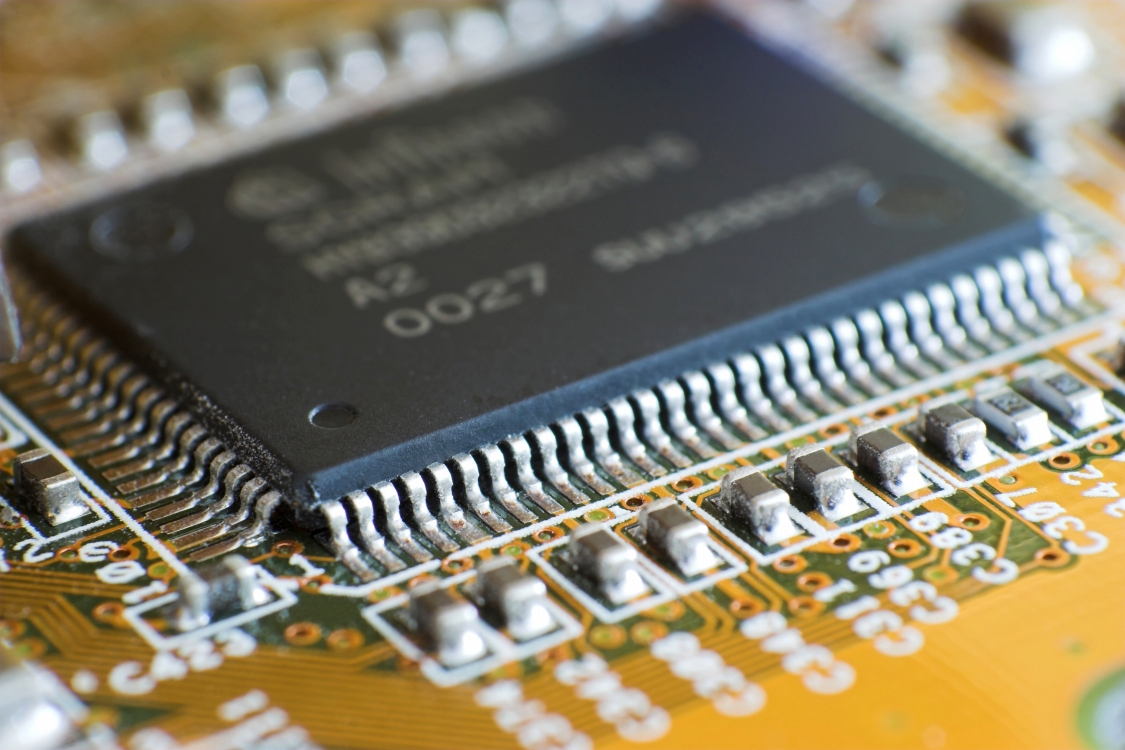

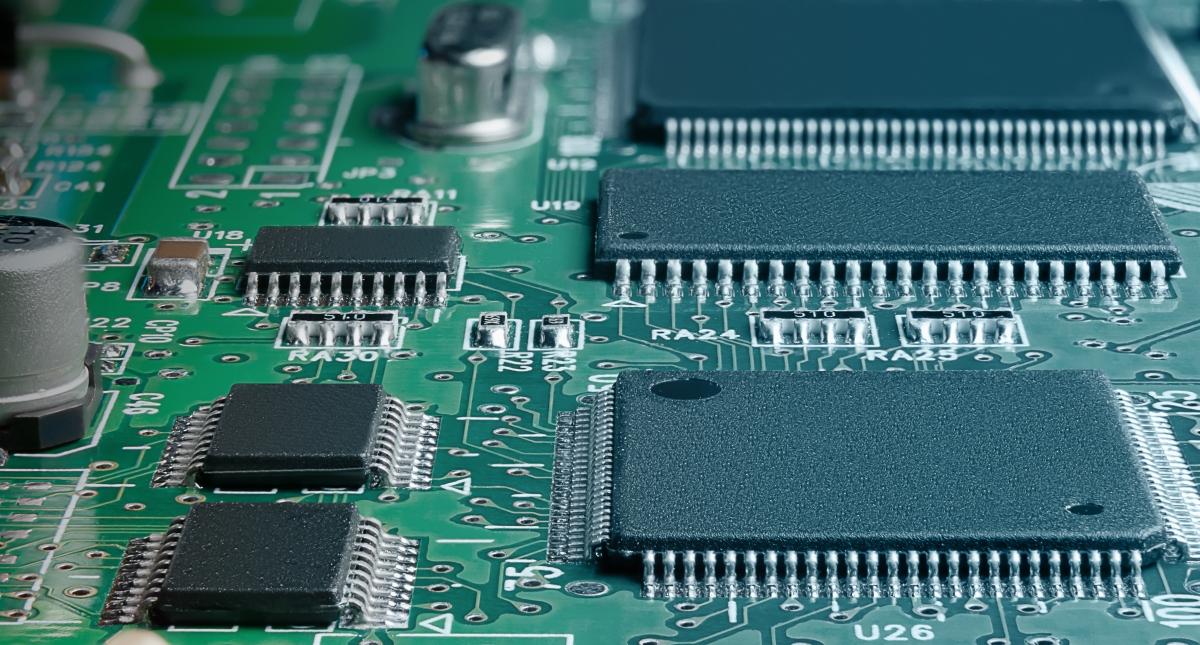

そこで、もうひとつの表面実装方式というのが登場してくるんだけど、これは部品の端子をプリント基板のランドに直接接続するというやり方で、貫通穴を使用せずに基板の表面だけで接続できるからその分スペースができて高密度化できる、というわけなんだ」

「なるほど、確かに表面実装方式のほうがリード線同士の間隔が狭くて本数が多いので、高密度に見えますね」

「そうなんだよ。ということで、本日のメインテーマは、この実装パッケージの変化についてだよ。ちょっとマニアックな世界に入っていくけど、頑張ってついてきてね。

1970年ぐらいからこれまで、プリント基板に実装される部品が劇的に変わってきたんだ。最初に登場したのは、『DIP(Dual Inline Package)』と呼ばれる実装パッケージ。Dualなので両側に縦に並んだ、髪の毛を解くクシのような形の脚があって、それをスルーホールに刺してはんだ付けする実装パッケージだね。

ただ、この方式は基板に穴を開ける必要があり配線効率が悪くなるので、穴を開けない実装方法が求められたんだ。その結果、表面実装方式が登場したんだよ。表面実装方式は基板表面のランドにはんだ付けする実装方法で、穴を開けないのですぐ隣の層も配線に使えるというメリットがあるんだ。両側タイプの『SOP(Small Outline Package)』と4方向にリードがある『QFP(Quad Flat Package)』タイプが存在するよ」

「ええっと…リード挿入実装方式のDIPと、表面実装方式は両側タイプがSOP、4方向タイプはQFPというんですね?整理しないと頭がこんがらがりますね」

「まだ序の口なんだけど、大丈夫かな?とりあえず、ガンガン進んでいくから分からなくなったら遠慮なく言ってね。

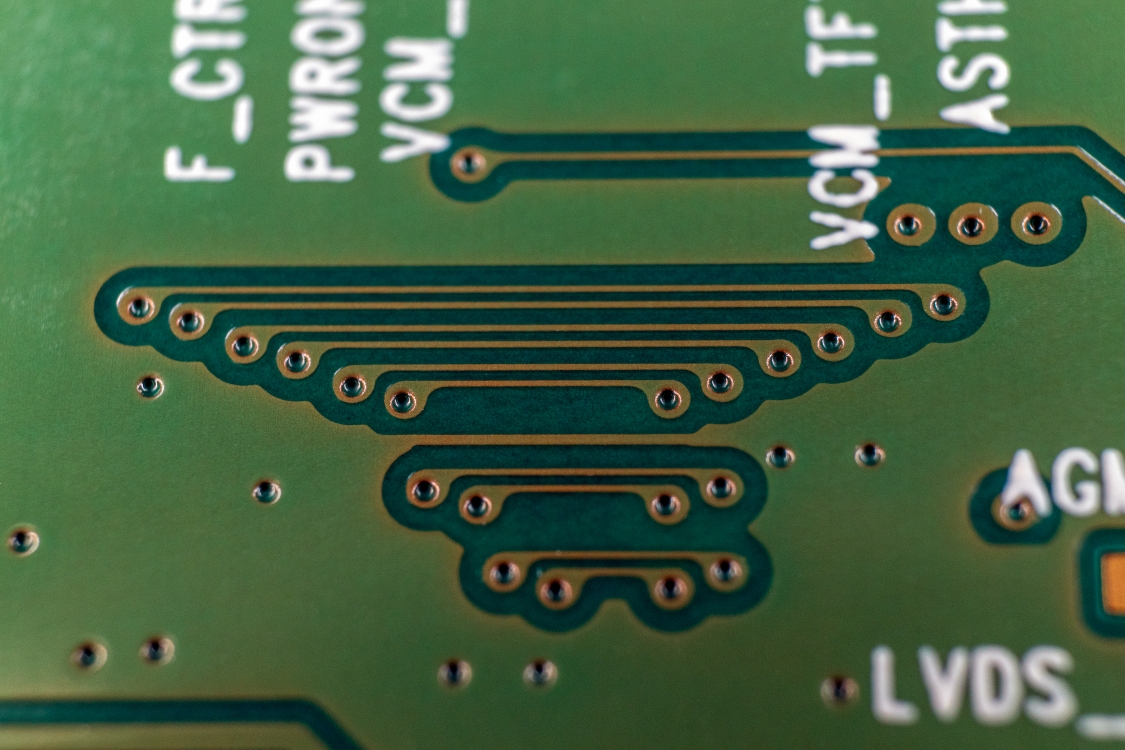

電子機器はそもそも小型化することが求められているから、基板の高性能化が進んで、配線のピッチもどんどん狭くなってきているよ。要求される機能が多くなればなるほど信号の出し入れをより多くしなければならないから、ピンの数が増えてそれに伴ってピッチも狭くなっているというわけなんだ。

例えば、リード挿入実装のピッチはもともと2.54mm、0.1インチだったものが、より小さいタイプになって2mm以下くらいになっている。引き回しをする関係でピンの間にも配線したいんだけど、ピン同士を詰めすぎると間に配線ができなくなるので、あまり詰めないようにしてピンの間に配線を何本通すかがポイントになってきているんだ。つまり配線仕様をピン間に1本配線にするか2本配線にするかで、線幅と配線間隔が変わってくるんだ」

「表面実装では、リードピッチはますます狭くなっていて、ピン間に通す配線はせいぜい1本くらいが限界だね。表面実装方式が導入され始めた1980年代後半では1.27mmピッチくらいだったのが、1mm、0.8mm、0.65mm、0.5mmと進んで、今は0.3mmくらいまでになっている。

例えば、高速道路とか車線の多い幹線道路をイメージするとわかりやすいと思うんだけど、ある信号を送ろうとした時に、あるエリアに配線が4本だけよりも8本とか16本あった方が、より多くの信号を速く送れるんだよ。

ただ、信号ピン数を増やすと実装する面積も増えてしまう。そして、部品の大きさが大きくなればなるほど基板も大きくなり、システムも大きくなってしまう。

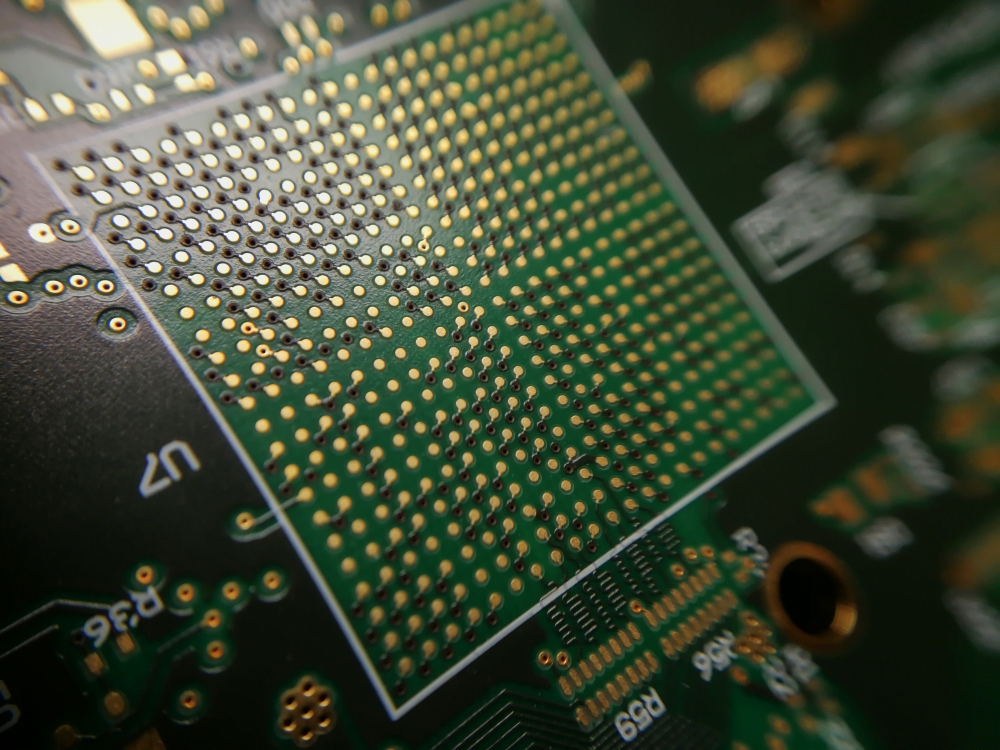

そこでだ。実装面積を変えずに信号ピン数を多くするために登場したのが『BGA(Ball Grid Array)』という実装パッケージなんだ。このBGA以降に登場するパッケージはもう基板の進化というよりは、半導体パッケージ基板の進化の話になってくるね。いかに小さくパッケージ化した部品を基板に載せるかがポイントなんだ。話を戻すと、BGAは実装部品の下にピンが格子状に『碁盤の目』のようになっているんだけど、鈴木君のような新入社員とか最近の若い人に、碁盤の目っていっても伝わるかな?」

「僕は『ヒカルの碁※1』という漫画を読んでたので、一応わかります」

「それなら大丈夫だね。

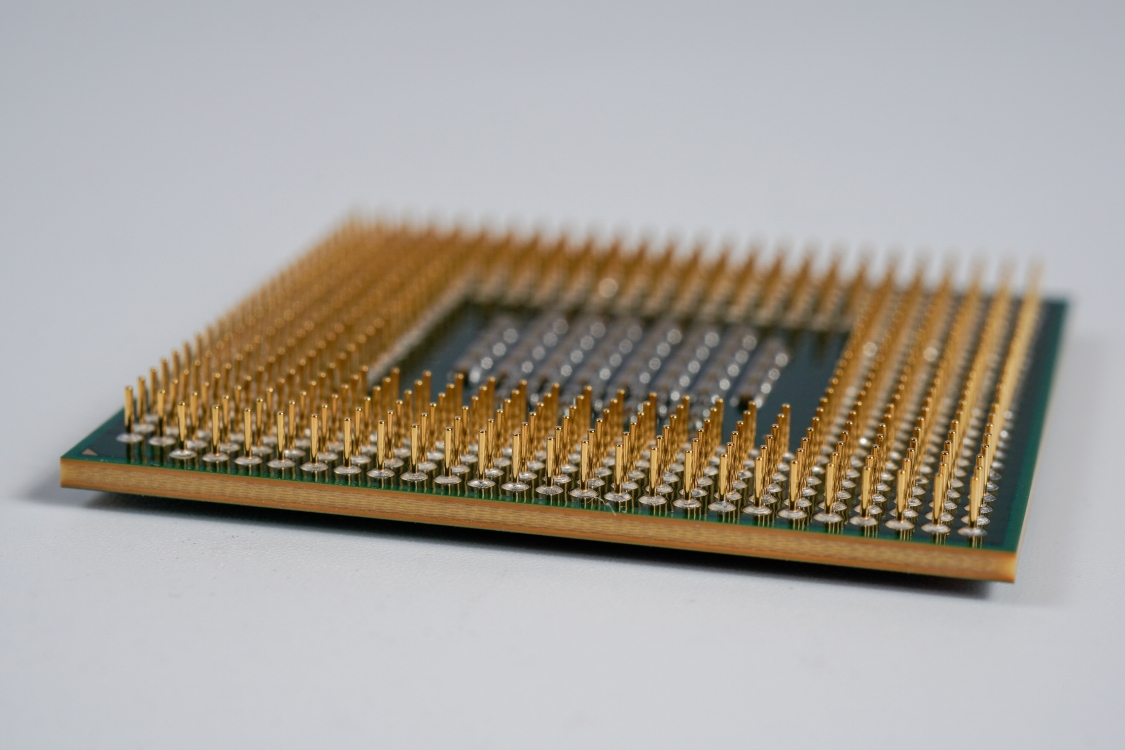

このBGAは表面実装方式の格子型と呼ばれてるんだけど、もうひとつ『PGA(Pin Grid Array)』というのがあって、これはリード挿入実装方式の格子型なんだよね。

DIP部品の脚が碁盤の目のようになっている感じで、要するにピンが格子状になっているんだ」

「さらに2000年頃には、親亀の上に子亀を乗せちゃえって感じで、背面にも電極を乗せて2階建てにした、『PoP(Package on Package)』という実装方式が登場したよ。複数の半導体パッケージを上下に積層する3次元実装パッケージだね。

また、同じ2000年頃、ひとつのパッケージ基板の上に複数の集積回路(Integrated Circuit)を入れちゃえって感じで、『SiP(System in Package)』という実装パッケージが登場したんだ。半導体の微細化の進展はインテル創業者のゴードン・ムーアが発見したムーアの法則※2というものでよく説明されるんだけど、回路線幅が10nm未満の世界では、さらなる微細化には多額のコストがかかるとされてるんだ。そこで、半導体そのものを微細化するのではなく、パッケージ基板上で半導体同士を接続する配線を形成して集積化するSiPの重要性が高まってきたんだ」

「ここまでの話を一旦整理すると、まず、プリント基板に対して実装部品を基本的にはすべてはんだで付ける。この時に穴を開けて付けるか、表面実装で付けるかで方式が分かれる。

同じ基板に同じ数の部品を載せる場合、穴が開いてたら片面にしか載せられないけど、表面実装形式だと両面に載せられるから、基板上で部品が占める面積を半分にでき実装密度が上げられるというメリットがある。

世の中の電化製品は多機能、高性能、小型化を求められる。高性能化によって回路規模が大きくなっていってしまう一方で、同時に小型化も求められているのでリード挿入実装方式から表面実装、BGA、PoP、SiPと実装方法が進化し、どんどん高密度化してきたんだ。いつか詳しく話すつもりだけど、基板の中に部品を埋める部品内蔵という実装技術もあるよ」

「もう覚えきれないぐらいの実装方式が登場したんですが、現在主に使われているパッケージはどのあたりなんでしょうか?」

「今日の説明で出てきた部品は全部まだ使われてるよ。でも、DIPはもうあまり使われていないかも。4ピン、8ピンぐらいの小さいDIPは見かけたりするけどね。PGAもほとんど使われなくなってるようだね。

必然性があるものは残っているけど、時代に合わないものは消えていってる感じかな。機能的、効果的でないもの、製造コストがかかるようなものは流行りが終わるとなくなっちゃうよね」

「例えば、スマートフォン(スマホ)にはどの実装パッケージが入ってるんですか?」

「スマホで最も使われているのは、『FO-WLP(Fan Out Wafer Level Package)』というものだね。PoPとかSiPもそうなんだけど、このFO-WLPはボディ構造が小さくて、小型パッケージとして非常に有効で、携帯機器を中心に採用されている。グローバルで生産されていて、開発も活発に行われているよ。

一方で、『FC-BGA(Flip Chip Ball Grid Array)』という実装パッケージがあるんだけど、こいつはFO-WLPよりも大きくて、パソコンとかでよく使われているね。高密度実装パッケージの中心的存在で、ビルドアップ基板というプロセスで広く製造されているパッケージなんだ。

さらには、これもFC-BGAと同様大き目のパッケージなんだけど『3D-SiP(3 Dimensional System in Package)』という実装パッケージも存在する。これは技術的にはできてるんだけど、つくるのにコストがかかるので、まだあまり活用されてないんだよね。

この3D-SiPよりもむしろ、FC-BGAのCPU基板の隣に、HBM(High Bandwidth Memory)という積層したメモリーの基板を置くっていうのが、現在の実装パッケージのトレンドだね。

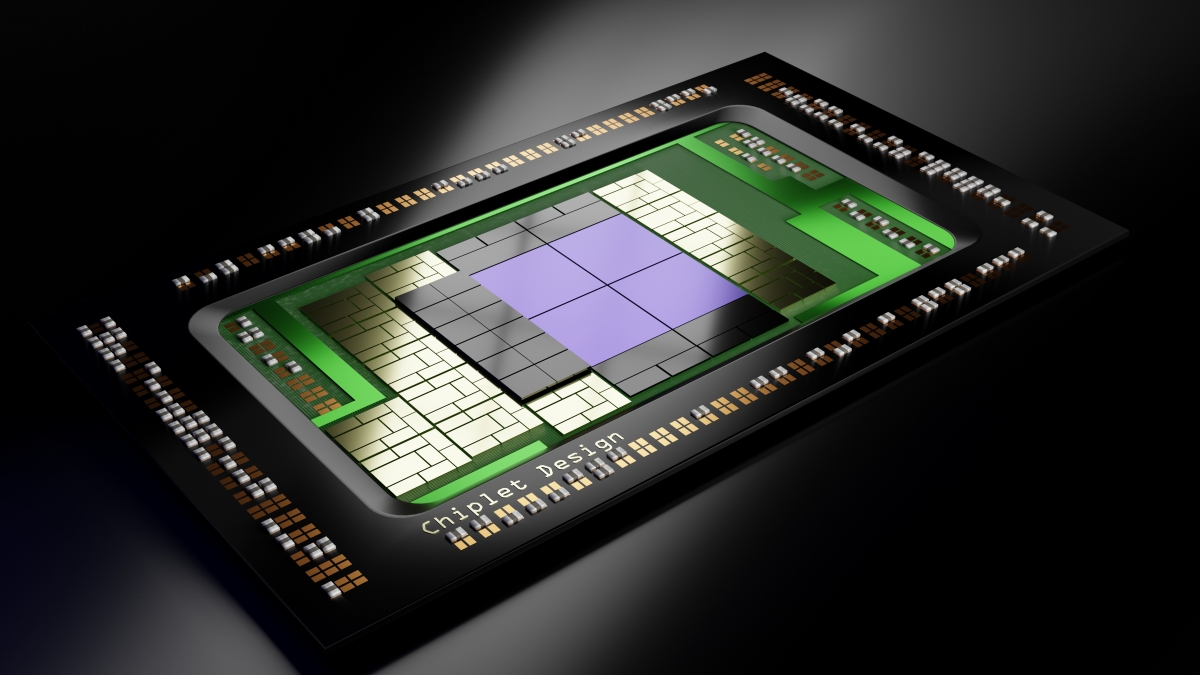

とはいえ、常に新しい技術は出てくるもので、最近はチップレットというのがこれからの技術として注目されているよ。チップとパッケージ基板の間にインターポーザーという、一般的なパッケージ基板より微細な配線が可能な中間基板を挟んで、それを媒介にチップ同士を接続したり、チップの上にチップを接合したりする実装パッケージなんだ。

半導体そのものの微細化がコスト面、性能向上面で限界にきているんだけど、最近の高度なAIの登場などで分析しなければならないデータ量は増加の一途をたどっていて、チップの大きさも拡大する傾向にあるんだ。

そこで、高度な演算を行う部分だけを最先端プロセスでつくり、必ずしも最先端プロセスを必要としない部分は成熟したプロセスでつくったものを組み合わせることで、全体として低コスト化を目指すというわけだ。チップレットのように異種チップを1つのパッケージにまとめるパッケージング技術を、ヘテロジニアスインテグレーション(異種チップ集積)というんだけど、近年すごく盛り上がっているんだよね」

「SiPと3D-SiP、そしてチップレット・・・何かどれも名前というか特長というか似たように感じるんですが・・・」

「うん、鈴木君は良い感覚してるね~。

そうだね、一旦整理すると、SiPは半導体とかいくつかの部品を一つのパッケージ上に実装したものなんだ。最初はそのパッケージにチップがひとつしか搭載されていなかったんだけど、平面上に何枚か搭載される時期を経て、省スペース化のために縦に3次元で積層した、3D-SiPというものに進化していったんだよ。このSiPが最近ではチップレットって呼ばれているんだよね。

呼称が変わるということはよくあって、その昔、HIC(ハイブリッドIC)と呼んでいたものが、MCM(マルチチップモジュール)と呼ばれるようになって、またそれがSiPと呼ばれ、直近ではチップレットとなり…、バズワードのようにその時々に応じたトレンドの言葉に変遷するのよ。ほとんど似たような実装の形態なんだけどね。

でもね、昔と比べて、3D実装の技術がかなりこなれてきたから、3D-SiPやチップレットが本格的な導入期に入ったのは間違いないと思うよ」

(続く)

※1 ヒカルの碁:ほったゆみ(原作)と小畑健(漫画)による囲碁を題材にした日本の少年漫画。『週刊少年ジャンプ』(集英社)にて、1999年2・3合併号から2003年33号にかけて連載された。

※2 ムーアの法則(Moore’s law):インテル創業者の一人であるゴードン・ムーアが、1965年に自らの論文上で唱えた「半導体の集積率は18か月で2倍になる」という半導体業界の経験則。

|

■参照文献 今回の連載企画では、2020 年 5月に発刊した『今日からモノ知りシリーズ トコトンやさしい 半導体パッケージ実装と高密度実装の本』の内容を参考にしています。 本書では、半導体パッケージの実装方法、部品内蔵基板の開発、高速伝送に対応した進化、プリント配線板の将来展望など、実装階層を構成する各種の高密度実装について、最新技術も含めて紹介されています。 なお、この書籍の著者の一人である長谷川清久氏が本連載を監修しています。 |

|

■監修者:長谷川 清久氏のプロフィール 1967年生まれ。1986年イビデン株式会社入社。 プリント配線板およびCOB基板、パッケージ基板設計、社内CAD・CAM開発業務に従事。 1994年イビテック株式会社に移籍。シミュレーション技術開発、高速・高周波設計技術開発、ノートPCおよび携帯電話、デジタルテレビ、プロジェクター、カーナビ、基地局向けの設計技術開発、メモリーモジュールおよび光モジュール、SiP、Si-IP、三次元積層IC、部品内蔵基板の設計技術開発を歴任。 2013年株式会社図研に入社。3D-ICおよび部品内蔵基板、3D-MID、Additive Manufacturing技術、IoT向けモジュールの設計環境構築業務に従事。 2023年Rapidus株式会社に入社。 |