技術情報コラム

高密度化する電子機器回路のテスト工程を大幅に向上!「不良が見える」バウンダリ スキャン・テストとは?

2018年07月25日※ このページの最後に『エレクトロニクス実装技術』寄稿記事PDFダウンロード用リンクがあります。

先月、東京ビッグサイトで開催された「2018 マイクロエレクトロニクスショー」にて、新設された “eX-tech2018” / バウンダリスキャンゾーンに出展しました。

この記事では、今回の新規出展の背景や、国内ではまだ認知度が高くないバウンダリスキャンの概要などを、本規格の普及や日本発標準化提案などを目的に設立された「バウンダリスキャン研究会」の幹事を務める 株式会社図研 EDA事業部 AIグループ 松澤 浩彦 に語ってもらいました。

バウンダリスキャン・テストの概要、そして近年、特に日本での対応状況について、あまり馴染みのない読者様にも解るように教えてください。また、今回バウンダリスキャン研究会として “eX-tech2018” へ出展することになった経緯もお願いします。

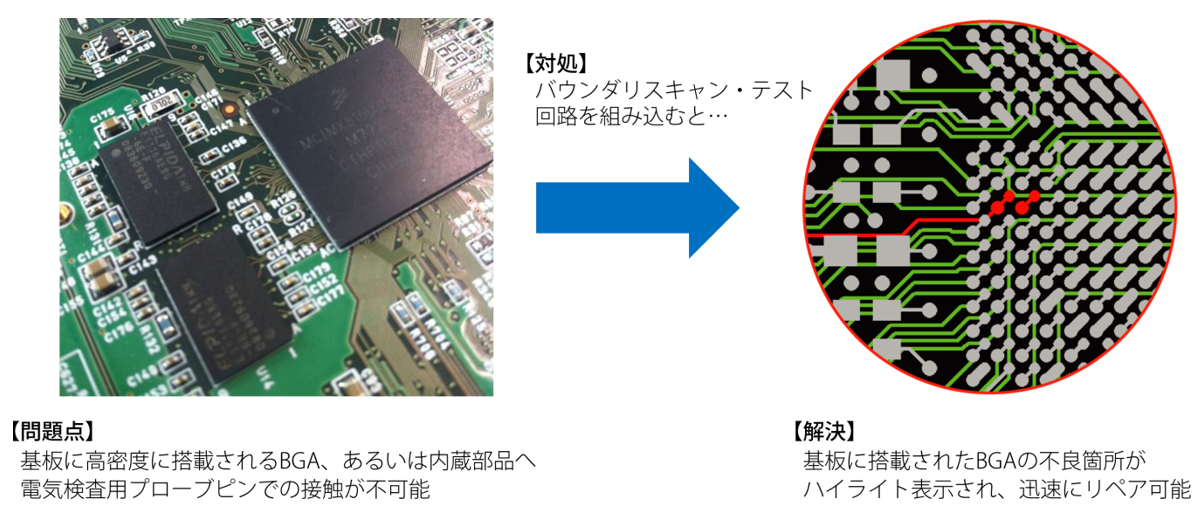

バウンダリスキャン(以降BS)の技術は歴史が古く、BGA(Ball Grid Array)実装が始まった1990年頃から、LSIに組込まれたテスト回路を利用して、電子回路アッセンブル後に電子デバイス間のインターコネクションを保証しようと始まりました。図研もその頃からCADにI/Fのソフトを開発して、活用度を高める取り組みをしてきました。

自動車の電動化などに伴い、部品内蔵基板やBGA/CSP搭載基板のような高密度な基板では、今までのようにボード検査のための検査パッドを設けることが難しくなったことから、既存の外部コネクタから検査したいという要望が挙がっています。その解決方法としてBSがあり、設計部門と検査部門とが連携することにより、効率良くBSテストができる様々なソリューションが提供されています。

しかし、国内外で顧客側とデバイスメーカ側とでの「リファレンス」という言葉の考え方の違いがあり、海外では「単なる参考情報 = Sample、”ご自身の判断でお使いください” というモノ」、一方日本では「メーカが公開するわけなので、自信を持って保証されるべきモノ」という捉えられ方をされがちです。こうした背景から、半導体メーカからのBSDL*1ファイルの提供が進んでいませんでしたが、ARM社などのスタンダードなLSIでサポートが開始されたことにより、一気に活用できるアプリケーションが広がりました。

とはいえ日本ではまだBSが広く認知されているとはいえず、そんな現状を打破すべく昨年起こしたBS研究会のアピールも兼ねて、5団体が出展し、設計・製造・検査現場のリサーチを行いました。

*1. Boundary Scan Description Language, BS素子内のテスト回路構成を記述したもの

図1:検査、不良解析の効率を大幅に向上させることができるBSテスト

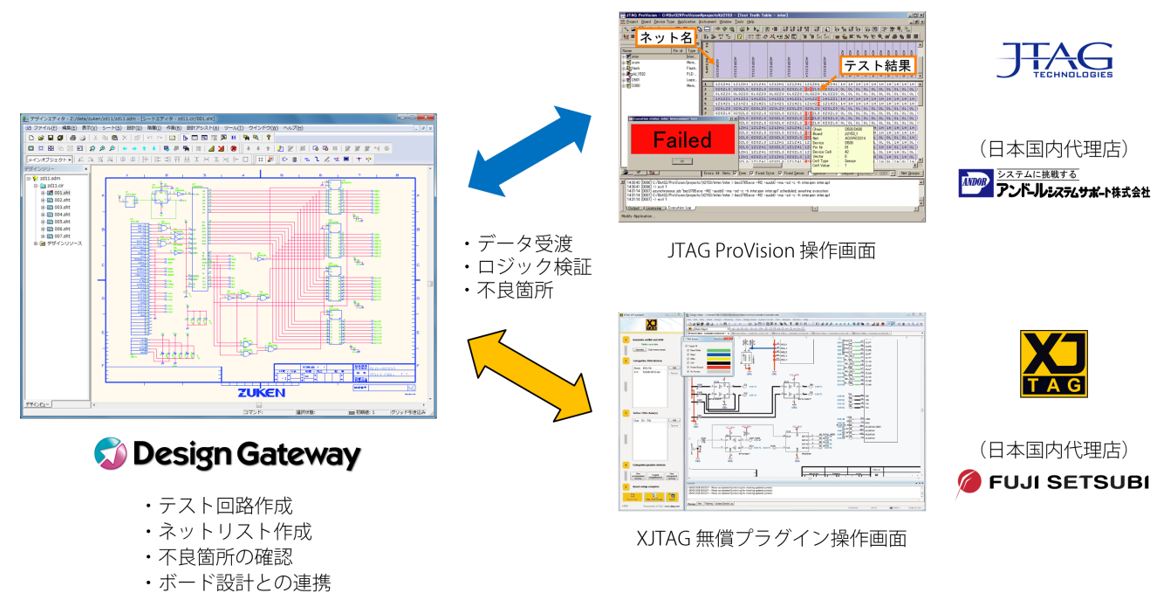

今回ブースで説明されていた内容についてですが、図研の Design Gatewayとベンダー各社のシステムとの連携で、どのようにテスト工程が効率化されるのでしょう?

まず、設計・開発のデバッグ時に、様々な要因が考えられるはんだ不良などの複合的な問題の切り分けが可能になります。BSにより基板全体のスクリーニングすることで、不良箇所を特定できます。この特定された部分だけを高精度なX線カメラを使って撮影することで、早期に原因究明ができます。

もちろん、提供されるテストライブラリが充実していると、テストプログラムの開発・保守の工数を軽減でき、設計・開発のデバッグから量産検査、不良解析にまで一貫して活用することができます。

従来の基板検査工程でのTATを短くするためには、より設計部門と検査部門とが協調して、BSテストに取り組むことで、AOIも含めた検査工程でのカバー率の向上が見込めます。

もちろん、提供されるテストライブラリが充実していると、テストプログラムの開発・保守の工数を軽減でき、設計・開発のデバッグから量産検査、不良解析にまで一貫して活用することができます。

従来の基板検査工程でのTATを短くするためには、より設計部門と検査部門とが協調して、BSテストに取り組むことで、AOIも含めた検査工程でのカバー率の向上が見込めます。

図2:ベンダー各社システムとの連携を強化し、シームレスな

テスト環境を提供するCR-8000 Design Gateway

テスト環境を提供するCR-8000 Design Gateway

また、『エレクトロニクス実装技術』2017年7月号に掲載された「DfT(Design for Testing)実現に向けたEDAの取り組み」記事PDFを、こちらからダウンロードしていただけます。

※ 記事データ提供協力:Gichoビジネスコミュニケーションズ株式会社様

【ご参考】

今回出展したBS研究会メンバー所属事業体のラインアップと出展概要、図研との関係などについて

1. 愛媛大学様:

BS研究会の亀山主査の所属大学です。検査技術を研究されています。今回は「アナログBSによる微小抵抗計測/三次元ICのTSV抵抗評価 」を紹介されていました。

2. 徳島大学様:

検査技術を研究されています。今回は「集積回路の遅延故障検出のためのTDC組込型BS設計」を紹介されていました。

幹事谷口様の所属する会社です。JTAG Technologies社(オランダ)の販売代理店で、「JTAGテストによるBGA実装基板の検査、故障診断と実装不良の改善手法」を紹介されていました。

図研のCRには、先方の「JTAG ProVision」とのI/Fがあります。

JTAGテストの基礎が分かる 入門セミナー<無料>

JTAGテスト お客様の導入事例集

図研のCRには、先方の「JTAG ProVision」とのI/Fがあります。

JTAGテストの基礎が分かる 入門セミナー<無料>

JTAGテスト お客様の導入事例集

4. 富士設備工業株式会社様:

XJTAG社(イギリス)の販売代理店です。

図研のCRには、先方の「JTAG BSテスター」とのI/Fがあります。

図研のCRには、先方の「JTAG BSテスター」とのI/Fがあります。

5. 株式会社図研:

BSテストへの新たな対応として、JTAG Technologies社、XJTAG社の製品との協調設計環境を紹介しました。