エッジAI開発に最適な「世界最小クラスのSoM」開発に、Design Forceが活躍!

2020年11月26日このほど、関西支社のお客様が Design Force で「小さいけどスゴイ」モノを作られた、との噂を聞きつけ、開発ベテランメンバーとともに大阪府は摂津市、株式会社近藤電子工業様の本社へ向かったのでした。

ご対応いただいたのは、大阪本社より自社製品プロジェクトのご担当役員、開発プロジェクトリーダー、PCBの全体責任者、オンラインにて横浜営業所より、機構・ハードウェアエンジニア、札幌営業所よりモジュールPCBのエンジニアという手厚い布陣。早速「小さいけどスゴイ」について、いろいろ伺っていくことにします。

エッジAIの新”芽”、KEImとは?

まずは名前なんですが、KEIm……ケイム?…「はい、呼称はケイムです。”KEIm”とは、Kondo Electronics Industryの頭文字と、ドイツ語で”芽”を表す”keim”を合わせたものです。ロゴマーク中央の”I”が茎となって、葉が伸びていく様子を示していまして、このロゴのように成長していってほしいという願いを込めています」と、製品担当役員の中村様。

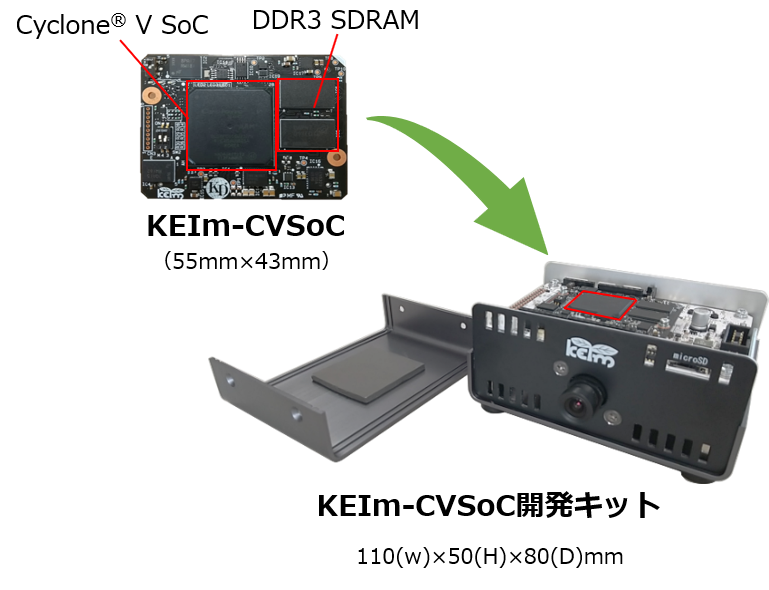

元々、10年ほど前から旧Altera代理店だった株式会社マクニカ アルティマカンパニーの支援で、Intel® MAX® 10 FPGAベースのシステム検証用ボードを開発していた同社。インテル社のデザイン・ソリューション・ネットワーク(DSN)にも参加しており、これまでKEImブランドでMAX® 10 FPGAベースの2製品を作ってきたのですが、量産対応モジュールが世の中にあまりないことに気づきました。「画像処理のエッジAI向けを狙ったSoM(システムオンモジュール)で、小中ロット量産まで対応可能なものを作れば、引き合いがあるんじゃないかと思いまして」。そうして生み出されたのが今回の「小さくてスゴイ」、KEIm-CVSoCというわけです。

ちなみに、製品名中の”CV”はインテル社FPGAのIntel® Cyclone® Vを表しており、近藤電子工業様ですでに導入済みだったCR-8000 Design ForceのKEImシリーズでの利用は、最も開発難易度が高かった今回のKEIm-CVSoCが初めてだったとのことです。

ではオススメポイントを…と訊いてみると、「まずは、55mm × 43mmという世界最小クラスのサイズを実現していることですね。製品自体の小型化に貢献できるものと期待しています。そして、DDR3など高速ボードでは苦労するポイントになる配線系がすでに結線してあるところです。また、画像処理を意識して作ってあり、インテル社のOpenVINO™に対応するなどAIとの親和性も高いので、まさにそういったエッジAIの開発を目指すにはうってつけなんです。」

なるほど、しかしてお値段は…「そこもポイントでして、SoC FPGAベースのAI画像処理評価キットは概ね1台あたり15~20万円くらいするんですが、当社のKEIm-CVSoC開発キットは、筐体込みで98,000円(AIアクセラレータ別)の予定です」。筐体付きのプラットフォームとしては画期的ですね! さらに、パートナー各社様のIPにも対応した、薄型タイプのAIカメラ開発キットも現在企画中で、お客様のさらなる量産化に対しても貢献できるとのことです。

さまざまなトレードオフ要件の落とし込みに苦労

せっかくなので、完成に至るまでのプロセスも伺ってみることに。まずは、この製品の開発要求事項のサマリです。「それは大変でしたよ。なにせ、世界最小クラスを目指したわけですし、後々量産可能とするためには安価にしなければなりません。さらに、電磁環境適合性(EMC)にも配慮しなければという特性上の要件もありますからね。それぞれ達成が難しい条件を複合的に勘案して、落としどころを探るのに相当苦労しました」と、モジュールPCB責任者の石川さん。

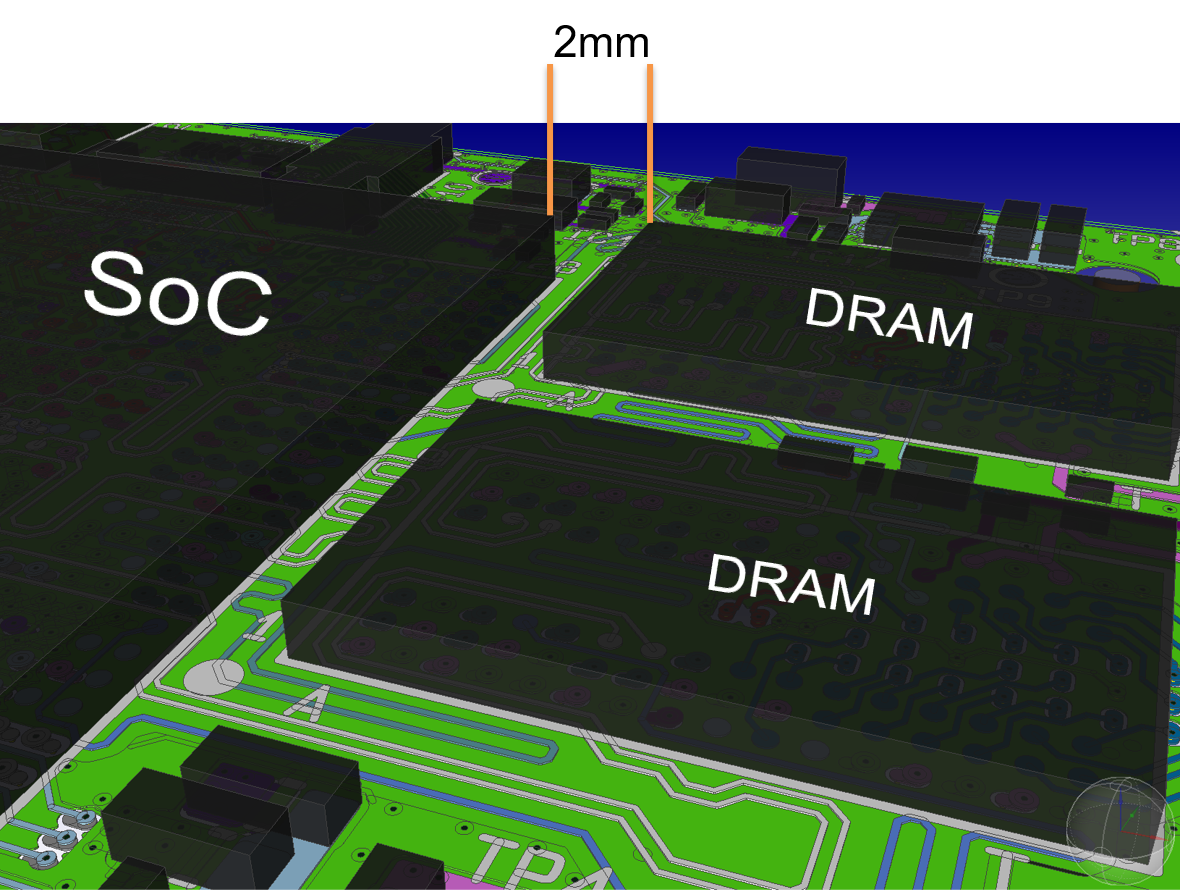

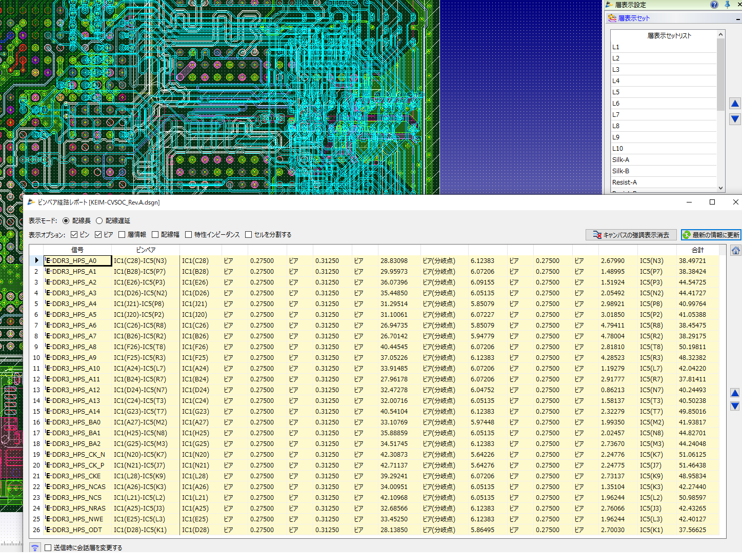

それで、解決の方向性としては…「まずは、高密度基板設計を可能にする工夫ですね。特性を維持するのが難しいDDR3は、データビットをSoC側でピン配変更して実装面積を最小限に、LVDSやその他GPI/OはSoC/コネクタ双方でピン配変更してレイアウトの最適化を徹底しました。当初コネクタのピン配はフリーだったのですが、ユーザー視点では順番に並んでいたほうが使いやすいだろうと判断し、自由度がなくなってしまいました。他にクロック負荷やバンク違いなどといったSoC制約上の懸案事項が発生しましたが、それらもレイアウト変更で対応しました。」

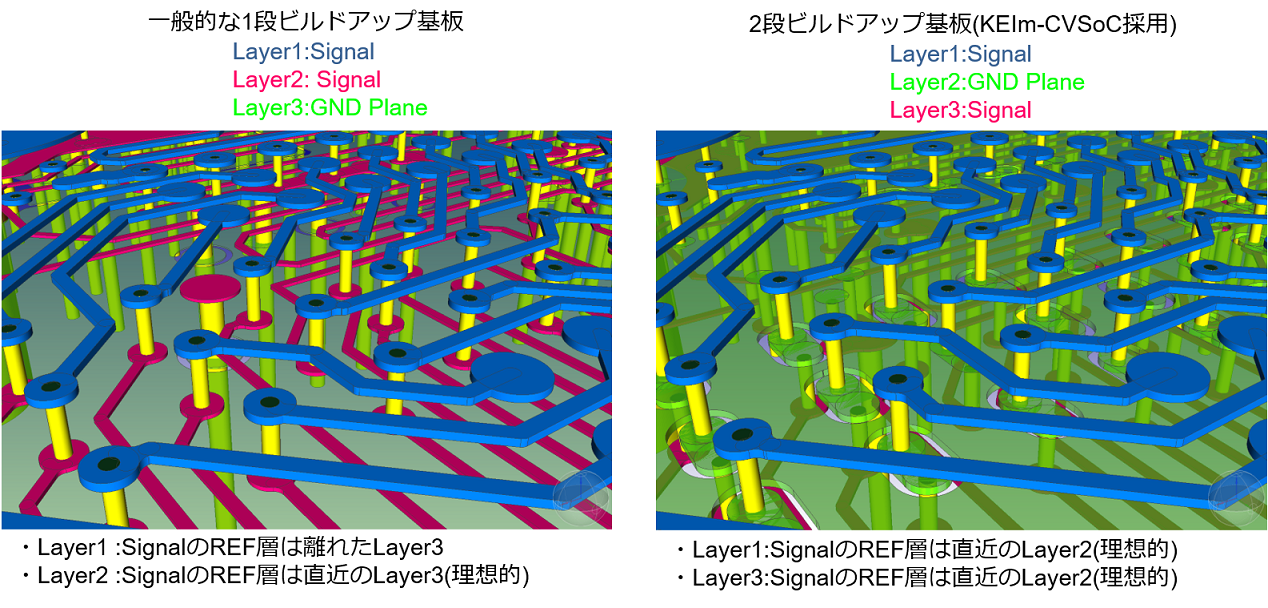

層構成についても、3段10層、2段12層、1段8層(さすがにこれはダメだろうという話になったそうですが)などいくつも候補があり、各層の配線インピーダンス値を計算してDDRや高速信号のフロアプランが成立するか、波形/実装面積の両面から解析/検討をしたそうです。「最終的には価格と性能(特にEMC)とのバランスから、10層2段ビルド(2-6-2ビルド)に決定しました。1段ビルド構成を見送ったのは、L1/L2が配線層となることで、L1からのEMIが増加し許容できないだろうと考えたためです。」

また、EMCなどの環境性能へのさらなる対策として、EMC Adviser EX を使用。KEImは短時間開発の要件もあり、社内リソースを活かしてSoM、I/O基板ともに複数名体制で設計にあたりますが、チームとして設計品質を一定以上に保つには、目視チェック以外にこういったチェックツールが役立ったそうです。

また、筐体においてはKEIm-CVSoC開発キットのコストダウンのために、ベースボディにArduinoシールドが入る大きさの標準品を選定したり、I/Oコネクタやファンなどは自由度が利くフロントパネルとバックパネルに割り付けたりといった工夫も施されました。モックアップは、3Dプリンターで複数パターンを製作し、使い勝手や課題を解決していったそうです。

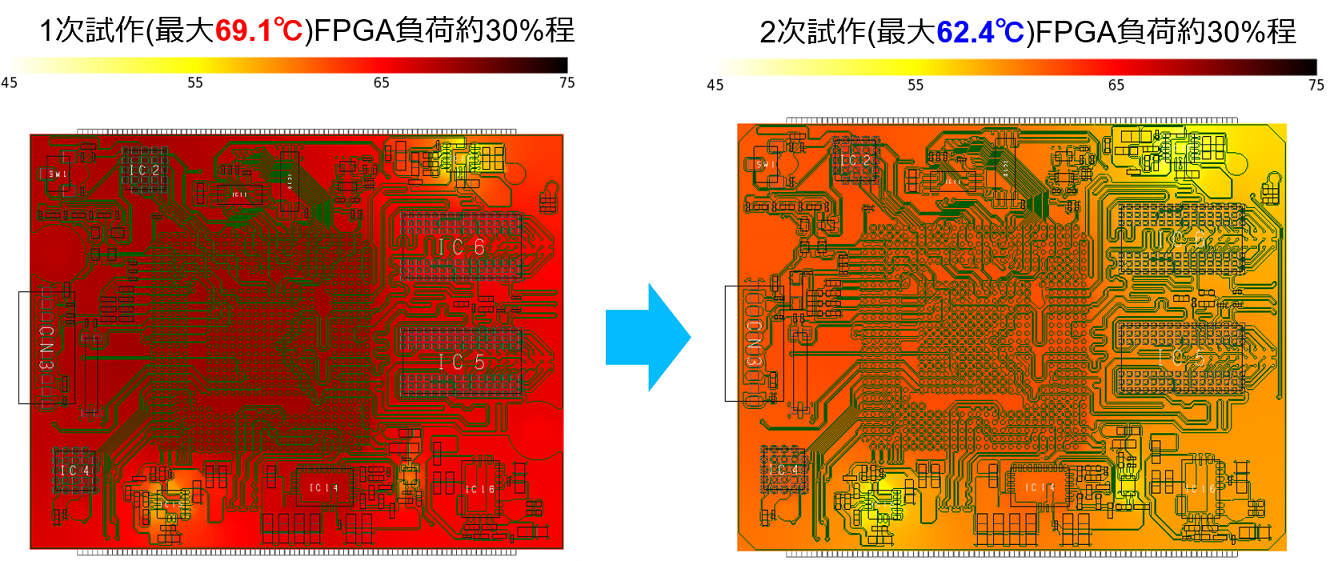

試作がアツアツに…

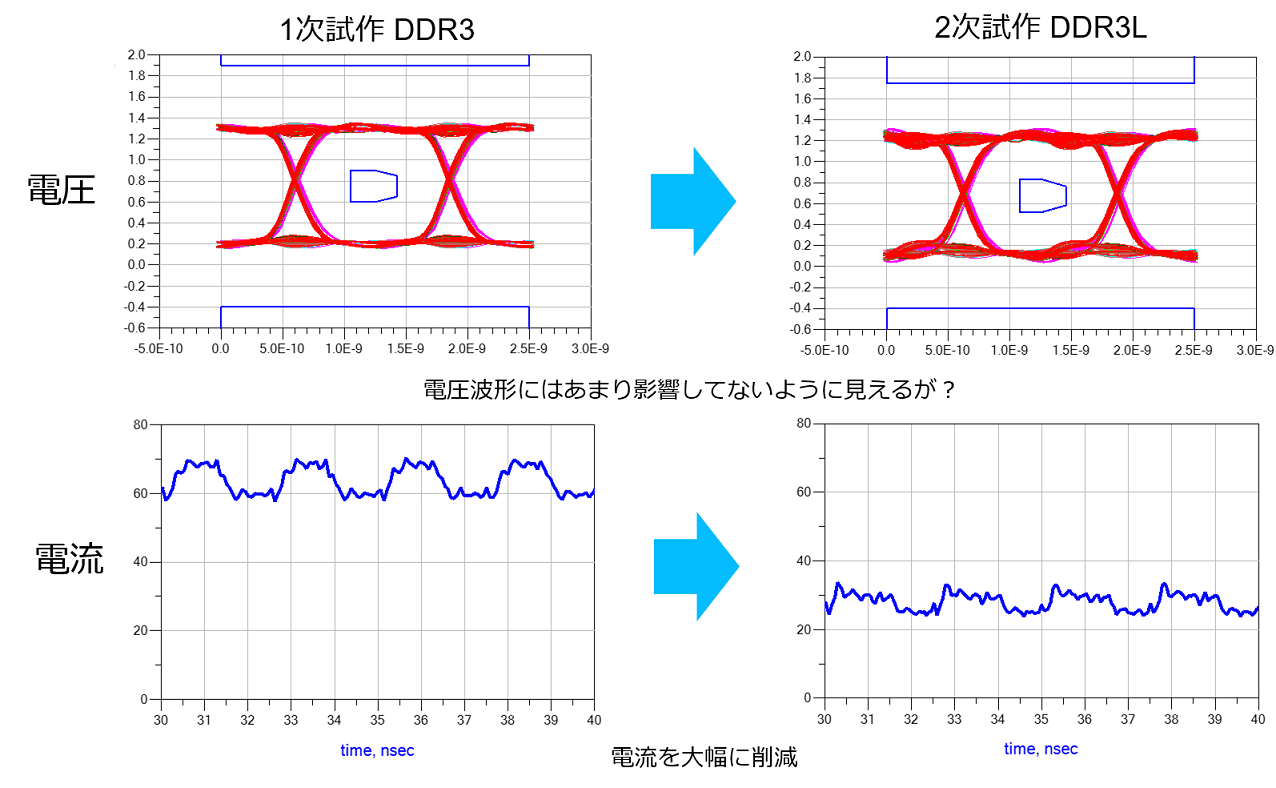

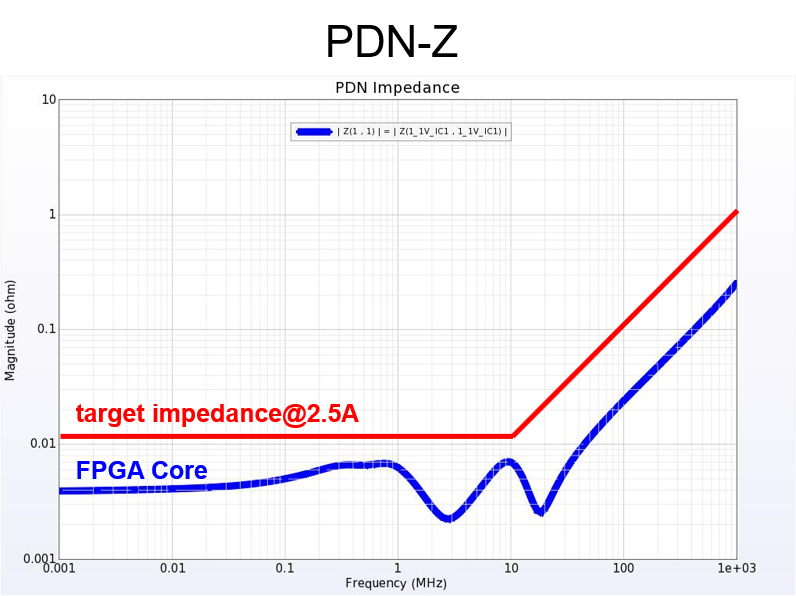

さて、仕様は決まっていざ試作となったわけですが、そう簡単にはできなかったようです。「一次試作では、熱が上がり過ぎてしまったんですよ」と石川様。「なので、まずはGNDを徹底的に増やしました。次にViaを増やして基板内での熱拡散を強化しました。純粋なPCB対策で下がったのは解析結果ベースで1.6℃です。まだ対策が必要ですから、次にDDR3 1.5VをDDR3Lとして1.35Vにしました。さらにはSoCの出力バッファ/終端定数を調整し、できるだけ電流を流さず信号品質を確保できるように工夫して、トータル6.7℃の効果予測を達成しました。振り返ってみれば、結果的にこれらの配慮はEMIの面で『巧い手法』だったと思います。また、SoCコア電源やDDR I/O電源など低電圧かつ単位時間当たりの電流変化の大きい電源はリスクがありますから、事前にPI解析を実施して特性を確認しました。」

KEImの設計は、やはりDesign Force!

気になる設計ですが、このKEIm-CVSoCの設計は CR-8000 Design Forceで行われたとのことで、振り返っていただきました。「そうですね、まずコンストレイントブラウザーによる配線長管理にずいぶんと助けられました。Cyclone® VとDDR3の等長部位の設計で最も活用したんですが、使い勝手がよく、首尾よく配線管理できました。特に、Design Forceのコンストレイントブラウザーは素晴らしいです。ICパッケージの長さの考慮、スキューグループ、DDR3×2枚の分岐トポロジーで効果を発揮しましたね。熱解析については、モジュール単体の結果ですが、ベースI/Oボードまで考慮し、マルチボードでやれたら、より便利だろうなと推察しています」。

近藤電子工業様では、現在開催中のインテル® FPGA テクノロジー・デイ2020 オンラインなどでKEIm-CVSoCを積極的にアピールされ、多くのご反響をいただいているとのことです。ご興味がおありの方は、ぜひ 同社のWebサイト をご覧になりお問い合わせください。

本キットを用いた開発は、筐体を含めたマルチボード設計となるため、熱やSIなどの課題もあります。図研としても Design Force によるマルチボード設計・検証や、エレメカ協調熱解析などをご提案できればと考えています。

さて、今回は「小さくてスゴイ」KEImの開発をフィーチャーしましたが、近藤電子工業様にはこれ以外にもさまざまな技術、幅広い対応分野、豊富なライセンスや拠点間連携ノウハウなどにより、多くのPCB受託実績があります。次回、KEIm-CVSoCの紹介しきれなかった内容や、Design Force を使ったチャレンジなどを含め、事例をご紹介いただきます。