会期後レポート

【ZIW2018】CR-8000 Design Gatewayロードマップ

2019年01月28日System Plannerに続いて、Design Gatewayの開発方針、リリース計画についてご紹介します。

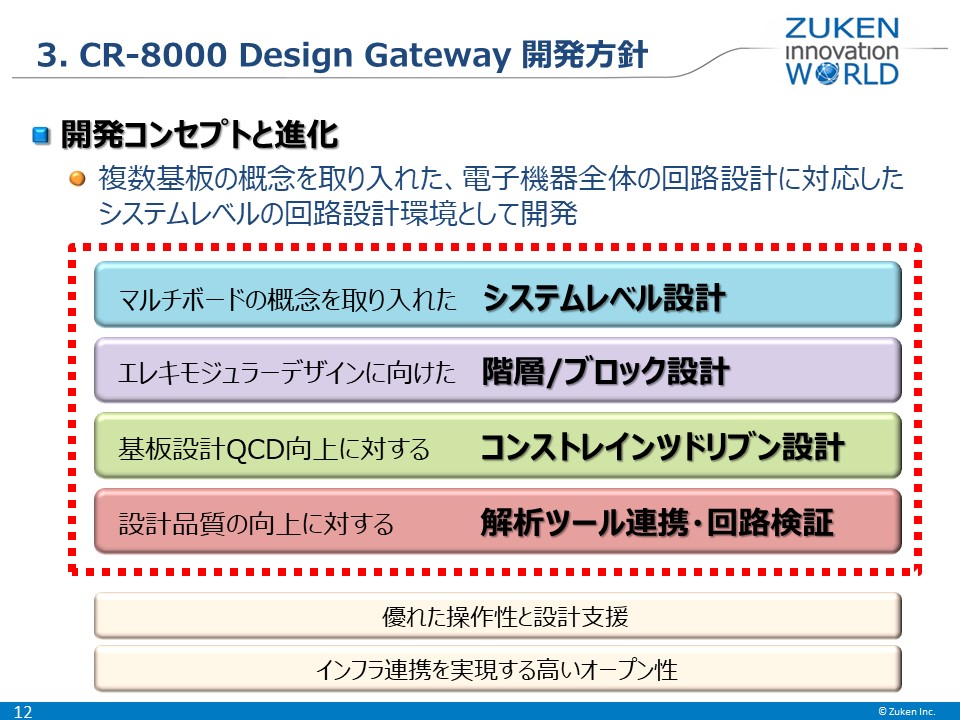

Design Gateway開発方針

Design Gatewayは、複数基板の概念を取り入れた電子機器全体の回路設計に対応したシステムレベル回路設計環境として、大きく次の4つの機能があります。マルチボードの概念を取り入れたシステム回路設計や回路検証を実現するシステムレベル設計、エレキモジュラーデザインに向けた階層/ブロック設計、基板設計QCD向上に対するコンストレインツドリブン設計、そして設計品質の向上に対する解析ツール連携・回路検証です。

今回のロードマップでは、それぞれの機能別に今後の取り組みをご紹介します。

今回のロードマップでは、それぞれの機能別に今後の取り組みをご紹介します。

システムレベル回路設計

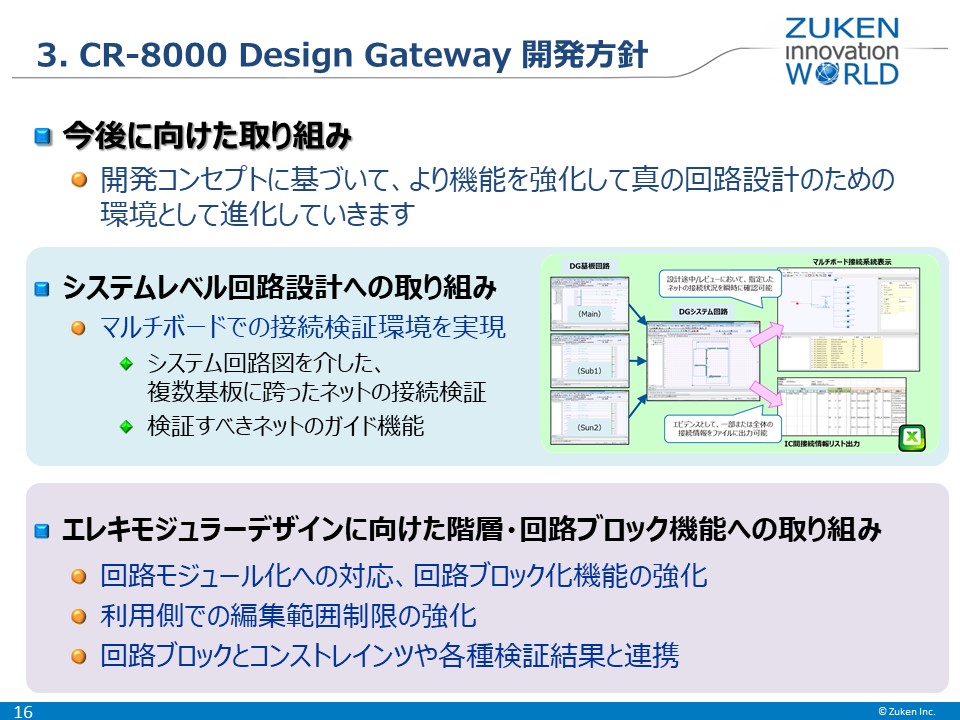

システムレベル回路設計では、複数基板から構成されるシステムに対して、基板間インターコネクトによる回路設計や基板をまたいだシステム全体の回路検証を支援しています。

今後は、マルチボードでの接続検証環境としての機能を強化し、システム回路図を介した複数基板にまたがる信号の接続検証環境を提供します。

今後は、マルチボードでの接続検証環境としての機能を強化し、システム回路図を介した複数基板にまたがる信号の接続検証環境を提供します。

エレキモジュラーデザインに向けた階層/ブロック設計

モジュラーデザインを推進し、回路ブロックのモジュールをIPとして、そのブロックを保証・担保する機能を拡張します。利用者側での回路ブロックの編集制限を部品単位でより詳細に設定できるようにする他、回路ブロックとペアで管理できる情報として、コンストレインツ(設計制約条件)に加えてブロック単位のDRC結果やサーキットアドバイザの結果との連携を実現し、製品設計に継承できるようにする予定です。

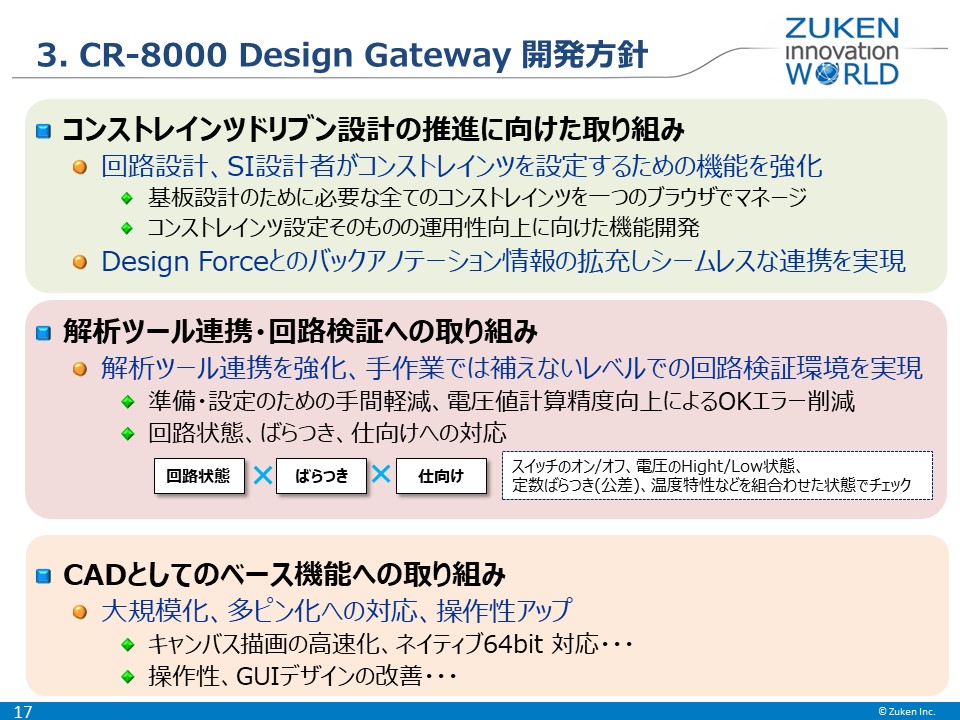

コンストレインツドリブン設計

コンストレインツドリブン設計は、基板への設計制約条件や設計指示を行い、それを守るように設計する手法で、回路設計者やSI設計者向けにブラウザから設定できるようにしています。

今後は、コンストレインツの設定機能を強化し、基板設計における必要なコンストレインツを一つのブラウザで設定、管理できるようにします。また、コンストレインツ設定もライブラリ化して容易に呼び出せるようにしたり、部品やピンが持つ情報を元に自動設定できるようにするなど運用性の向上も図ります。

今後は、コンストレインツの設定機能を強化し、基板設計における必要なコンストレインツを一つのブラウザで設定、管理できるようにします。また、コンストレインツ設定もライブラリ化して容易に呼び出せるようにしたり、部品やピンが持つ情報を元に自動設定できるようにするなど運用性の向上も図ります。

解析ツール連携・回路検証

設計品質の向上に向けた解析ツール連携・回路検証として、SPICEと連携し、部品やネットに設定した電気的な情報を元に、電気特性を考慮したルールベースのチェックができるサーキットアドバイザと、ツールではエラーが判定できないナレッジやノウハウを元にした定性的なチェックができるCircuit DR Naviを提供しています。

サーキットアドバイザでは、2つの観点での機能強化を進めていきます。

1つ目は、電圧値などの計算精度の向上と、そのために必要となる多くの電気的情報の設定負荷の軽減です。

2つ目は、回路状態 × ばらつき × 仕向けの組み合わせへの対応です。回路状態とはスイッチのオン/オフ、電圧のHigh/Lowなどで、それに定数のばらつき、温度特性などを組み合わせると、手作業による検証が困難ですが、その膨大なパターンのチェックに対応した回路検証環境の実現を目指します。

1つ目は、電圧値などの計算精度の向上と、そのために必要となる多くの電気的情報の設定負荷の軽減です。

2つ目は、回路状態 × ばらつき × 仕向けの組み合わせへの対応です。回路状態とはスイッチのオン/オフ、電圧のHigh/Lowなどで、それに定数のばらつき、温度特性などを組み合わせると、手作業による検証が困難ですが、その膨大なパターンのチェックに対応した回路検証環境の実現を目指します。

【Design Gateway 2018.0】について

2018年3月にリリースしたDesign Gateway 2018.0 では、上記の開発方針に基づき様々な機能拡張を行っています。

まず、コンストレインツ設定のブラウザをこれまで Design Force 用と Board Designer 用といった見た目や操作性が異なるブラウザに分かれていましたが、これを一つに統合し、操作性や運用面の改善をしています。

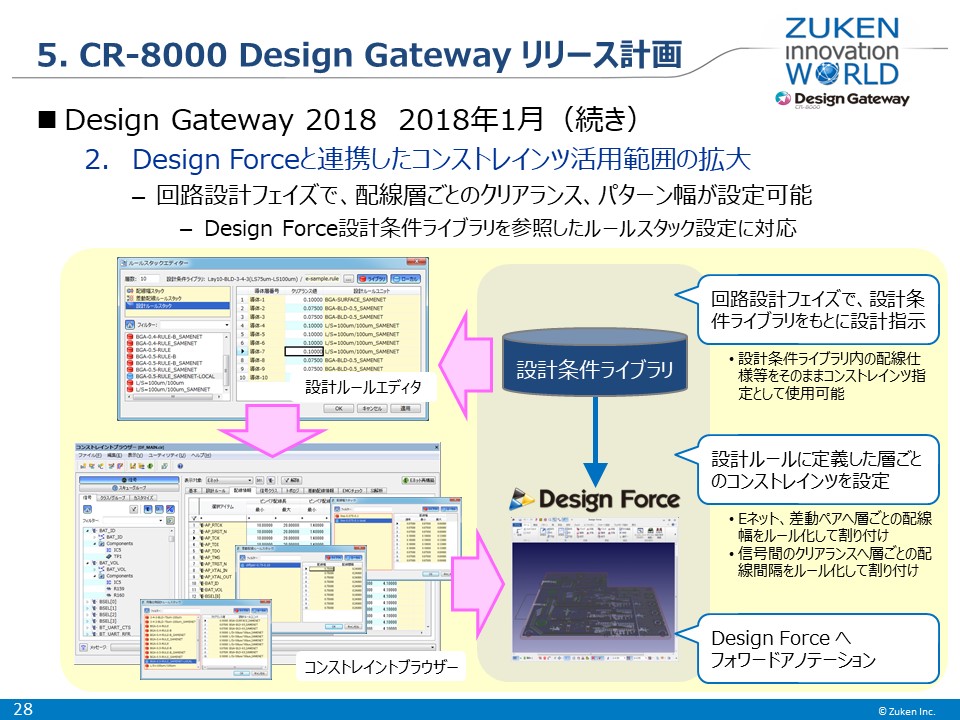

また、 Design Force と連携したコンストレインツの活用範囲を拡大し、回路設計段階で配線層ごとのクリアランスやパターン幅の設定できるようにしています。Design Forceの設計条件のライブラリを直接参照し、Design Force にスタック情報としてフォワードアノテーションできるようにしています。

まず、コンストレインツ設定のブラウザをこれまで Design Force 用と Board Designer 用といった見た目や操作性が異なるブラウザに分かれていましたが、これを一つに統合し、操作性や運用面の改善をしています。

また、 Design Force と連携したコンストレインツの活用範囲を拡大し、回路設計段階で配線層ごとのクリアランスやパターン幅の設定できるようにしています。Design Forceの設計条件のライブラリを直接参照し、Design Force にスタック情報としてフォワードアノテーションできるようにしています。

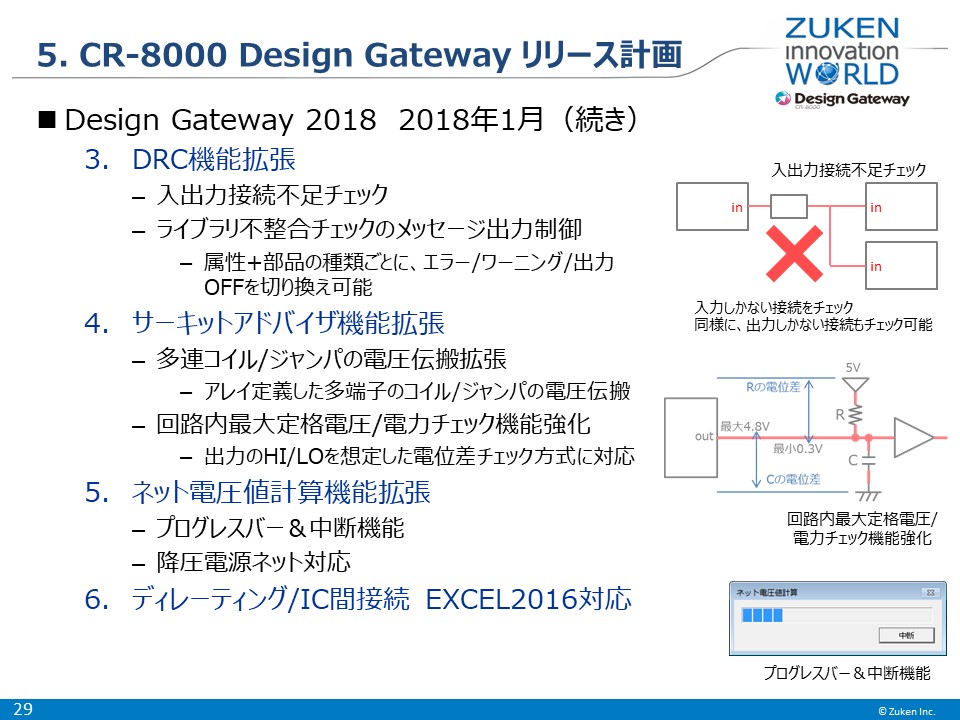

サーキットアドバイザの回路検証機能の拡張として、定格チェックで使用するネット電圧の伝搬処理において、多連コイルやジャンパにも対応しています。また回路内最大定格の電圧/電力チェック機能を強化し、出力のHigh/Lowを想定した電位差チェック方式に対応しています。

ネット電圧値計算の機能も拡張とし、他電源からの抵抗やレギュレータの降圧に依存する電源ネットもSPICE計算の対象としています。

ネット電圧値計算の機能も拡張とし、他電源からの抵抗やレギュレータの降圧に依存する電源ネットもSPICE計算の対象としています。

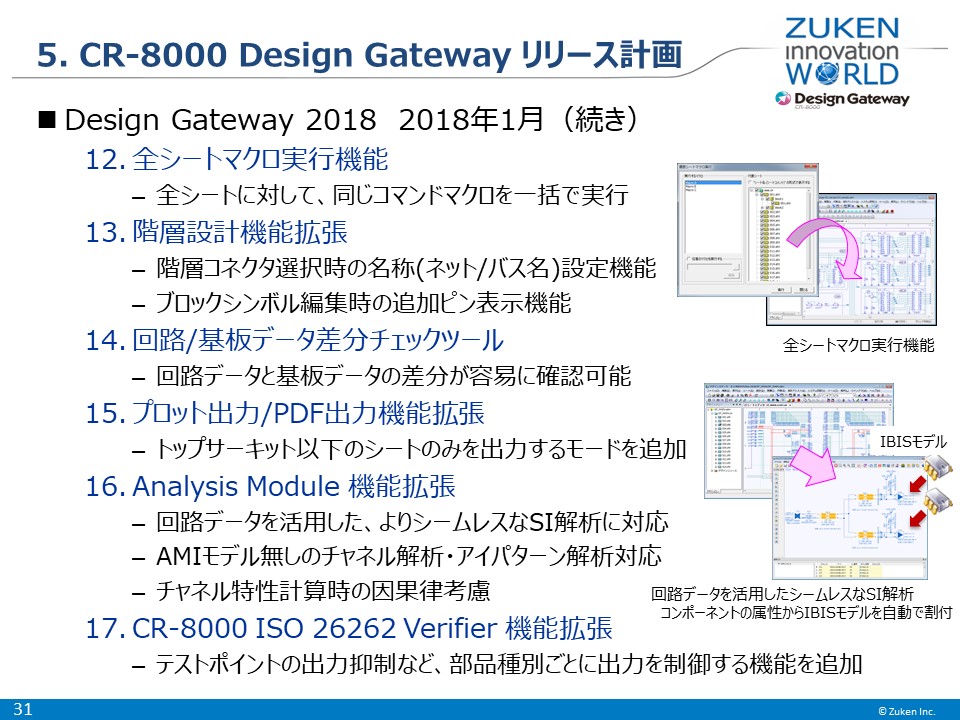

多くのお客様からご要望いただいていた全シートのマクロ実行にも対応し、階層内のすべてのシートに対して、マクロ実行ができるように拡張しました。

その他に、全シート対応としたオブジェクト検索機能の拡張や仕向け設計を考慮した部品属性比較ができるコンポーネントブラウザ機能拡張など、CADとしての基本機能も数多く強化しています。

その他に、全シート対応としたオブジェクト検索機能の拡張や仕向け設計を考慮した部品属性比較ができるコンポーネントブラウザ機能拡張など、CADとしての基本機能も数多く強化しています。

【Circuit DR Navi 2018.0】について

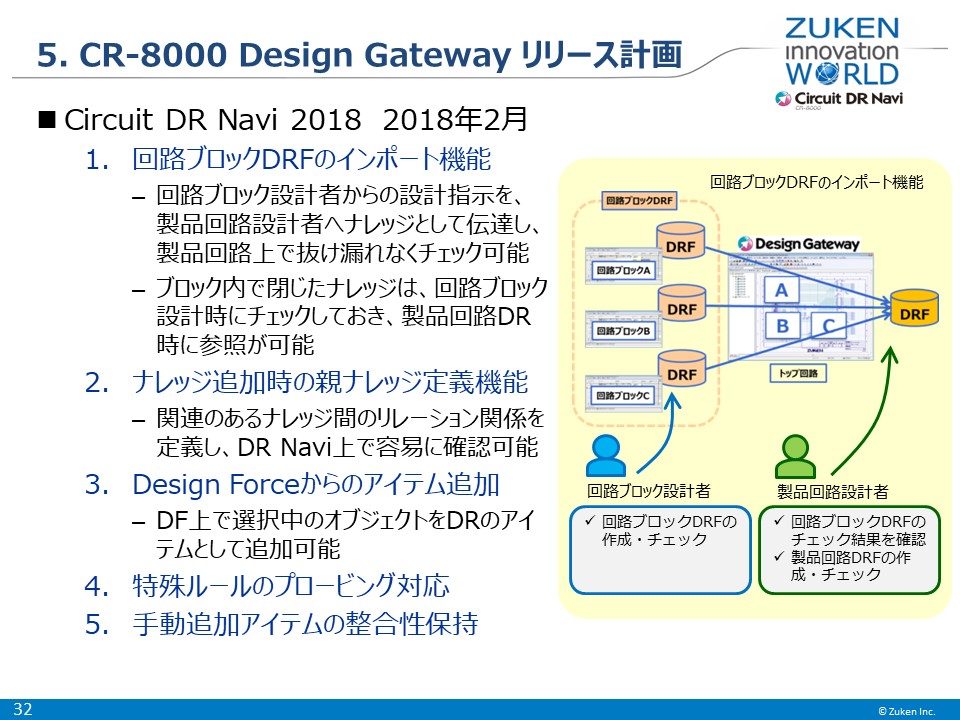

回路ブロックDRFのインポート機能において、回路ブロックとCircuit DR Navi のナレッジをペアで管理し、回路ブロック設計者から製品回路設計者へと設計指示を伝達できるようにすることで、抜け漏れなくチェックができるようにしています。また、Circuit DR Navi の対象範囲を広げ、Design Force上で選択したオブジェクトもDRのアイテムとして追加できるようにしました。

【Design Gateway 2019.0】について

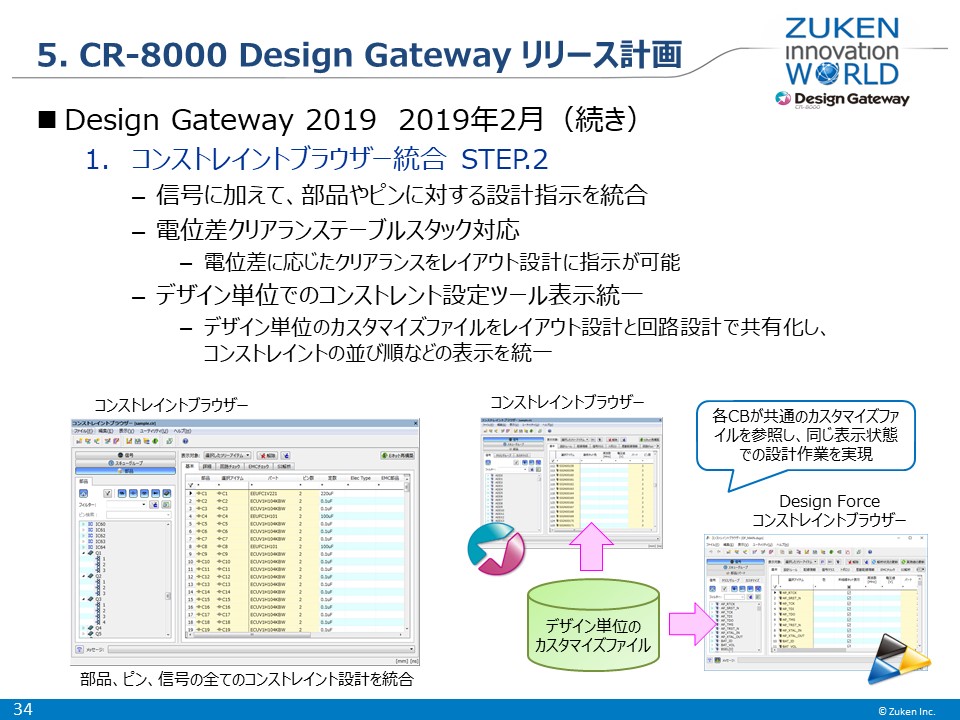

回路設計者とSI設計者向けの統合環境に向けたコンストレインツ設定ブラウザの統合として、2018.0に引き続き、STEP2として機能拡張します。ネットに加えて部品やピンに対する設計指示を統合し、配線、部品、ピンのすべてのコンストレインツ設定が1つのブラウザ上で設定できるようにする予定です。また、電位差に応じたクリアランスをレイアウト設計に反映できる機能や回路設計とレイアウト設計でコンストレインツブラウザの表示項目や並び順を共有することができるようにします。

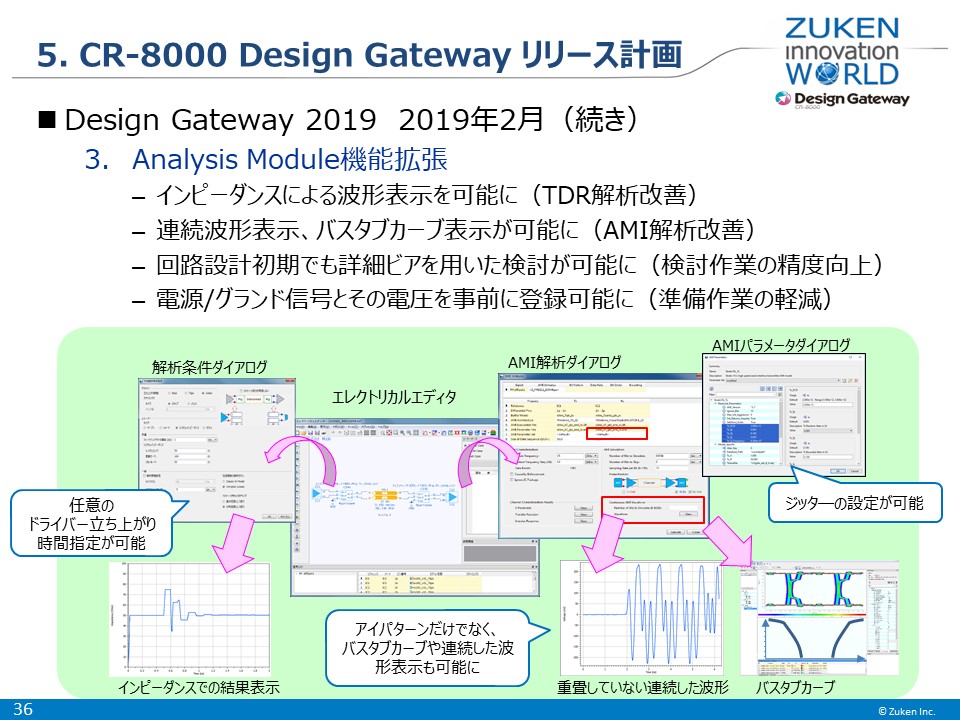

SI解析 Analysis Module の機能拡張として、インピーダンスによる波形表示をできるようにしたTDR解析改善や、連続波形表示やバスタブカーブ表示できるようAMI解析改善も行っています。その他、回路設計の初期段階でも詳細ビアを用いた高精度の検討が可能になるほか、電源やグランド信号とその電圧を事前に登録できるようにし、準備作業の軽減を図ります。

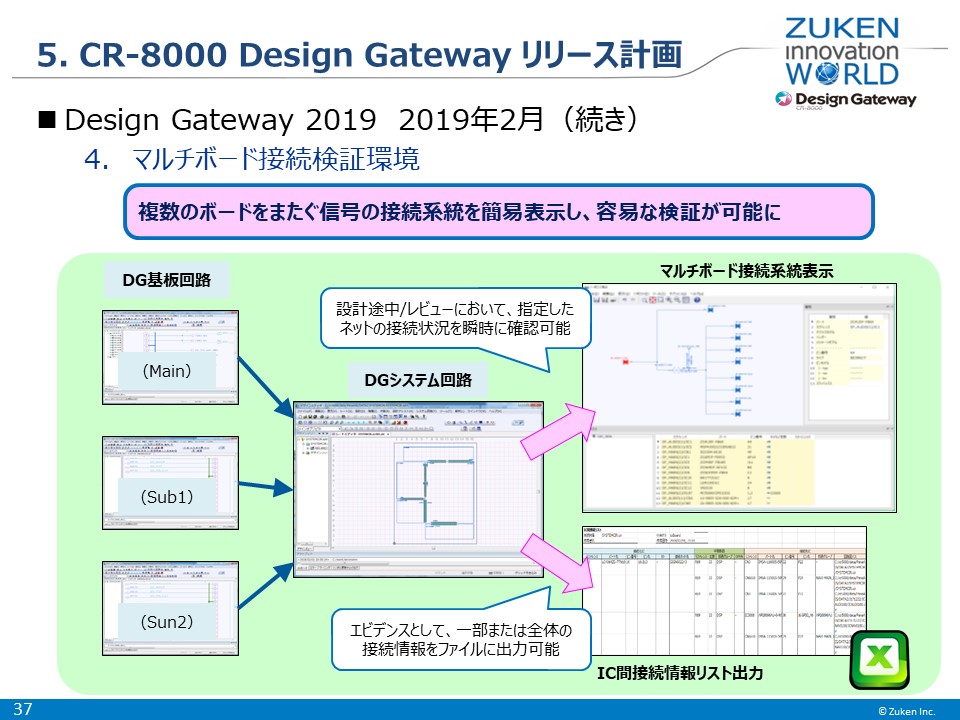

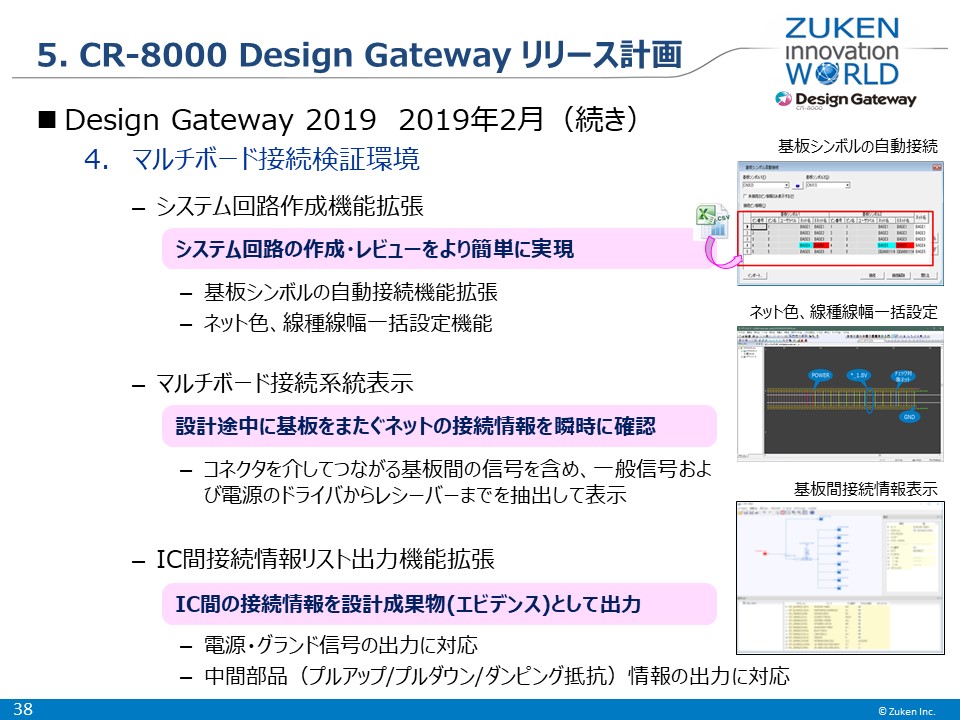

マルチボード接続検証において、新機能を提供する予定です。複数の基板にまたがる信号の接続系統を簡易表示し、設計途中のデザインレビューの際に回路やシステム全体の接続検証が簡単に行える環境を新しくリリースします。

また、マルチボード接続検証の回路作成・レビューを支援する機能として、システム回路上で検証に着目すべきネットを、ネット名や属性、もしくは接続先の基板の回路のピンペア数などを元に、ネット色や線種、線幅を一括設定できるようにします。

さらに、複数基板をまたぐ接続系統表示を可能にします。これは選択したネットに関するドライバからレシーバまでを抽出して系統図のように表示する機能です。ここから Design Gateway へのクロスプロービングも行えるようにする予定です。

さらに、複数基板をまたぐ接続系統表示を可能にします。これは選択したネットに関するドライバからレシーバまでを抽出して系統図のように表示する機能です。ここから Design Gateway へのクロスプロービングも行えるようにする予定です。

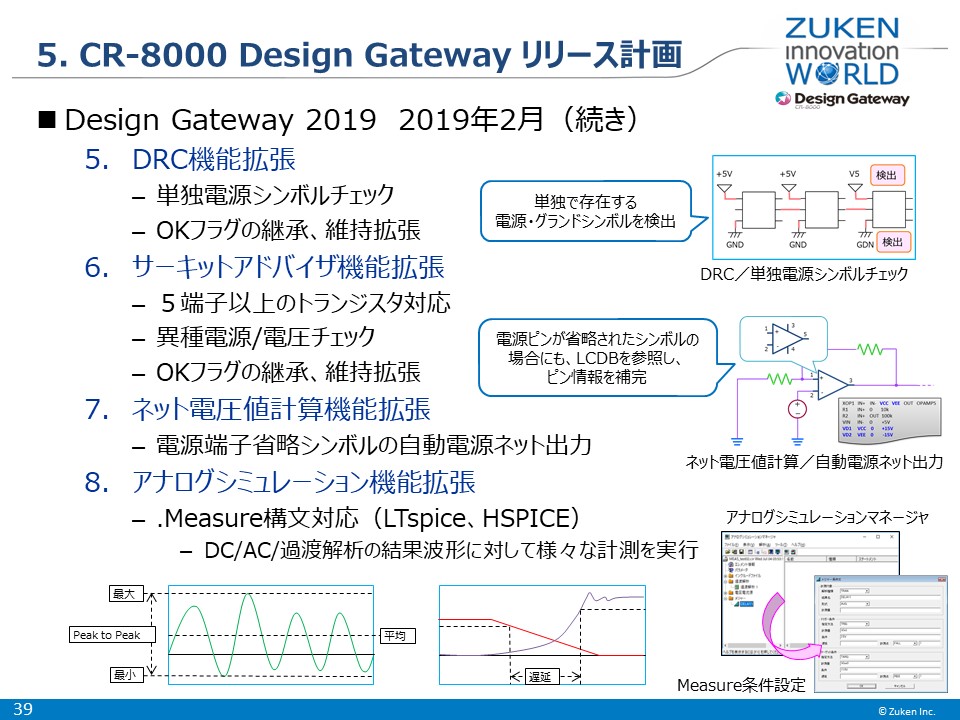

サーキットアドバイザでは、5端子以上のトランジスタ対応などの機能拡張を行います。

ネット電圧値計算機能では、例えばオペアンプのように電源端子が省略されているシンボルからも電源ネットを自動出力できるようにする予定です。

アナログシミュレーション機能も拡張し、SPICEのMeasure構文に対応します。波形のピーク・トゥー・ピーク測定や過渡解析結果を集計し、回路図検証で利用できるようにする予定です。

ネット電圧値計算機能では、例えばオペアンプのように電源端子が省略されているシンボルからも電源ネットを自動出力できるようにする予定です。

アナログシミュレーション機能も拡張し、SPICEのMeasure構文に対応します。波形のピーク・トゥー・ピーク測定や過渡解析結果を集計し、回路図検証で利用できるようにする予定です。

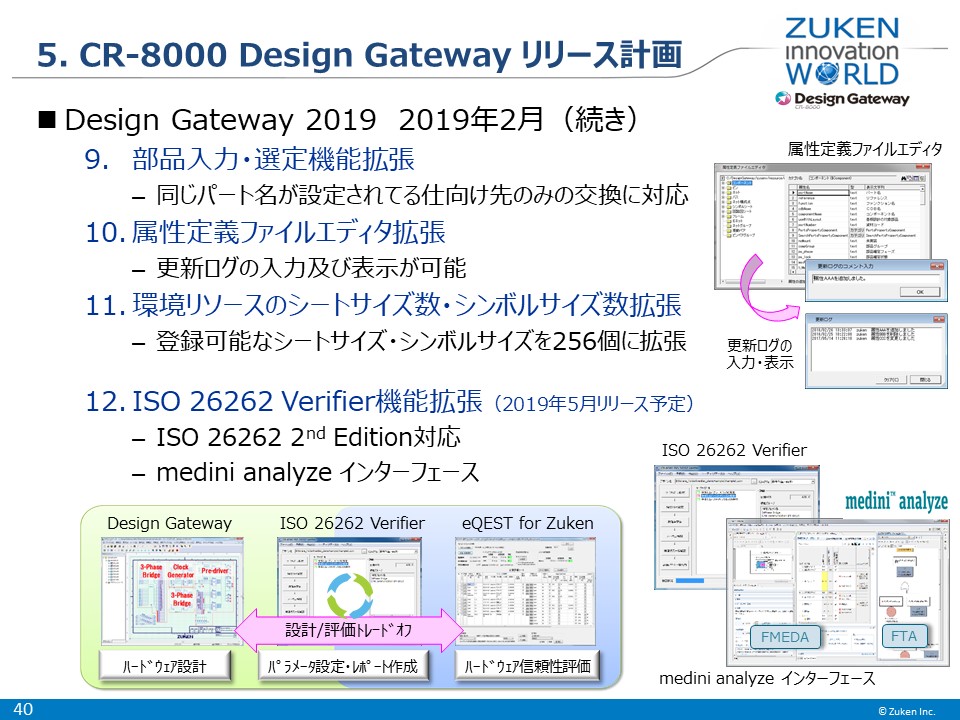

ISO 26262 Verifier機能では、ISO 26262 Second Edition への対応を予定しています。またmedina analyzeとのインタフェースも追加し、現在 eQEST for Zukenで対応しているFMEDAに加えて、FTAなどの安全分析手法にも対応する予定です。

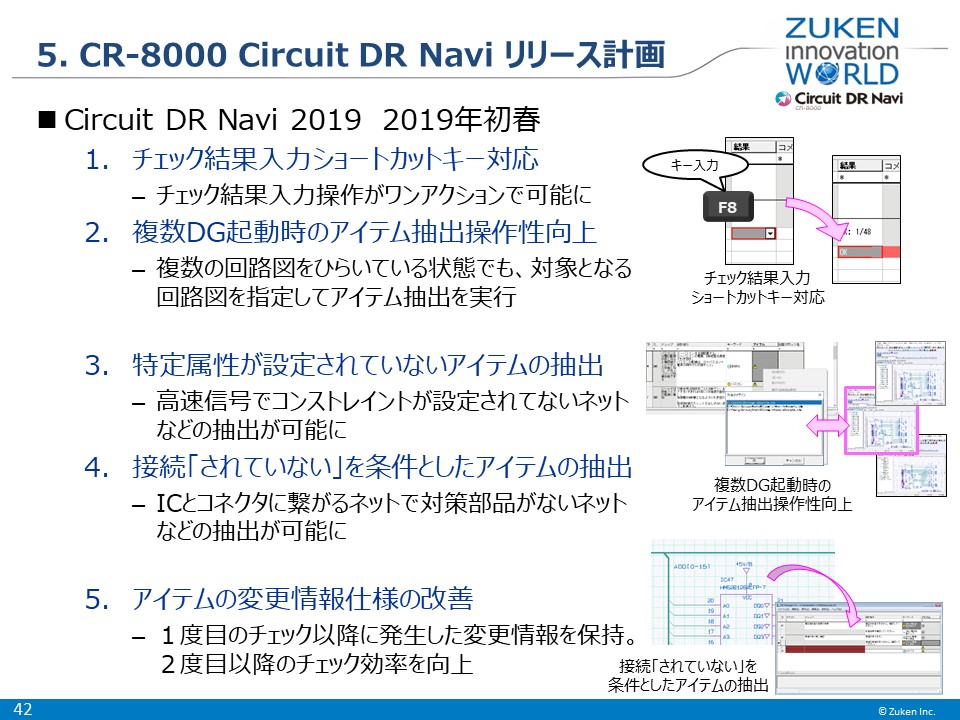

【Circuit DR Navi 2019】 について

Design Gateway で複数の回路図を開いている状態でも、対象とする回路図を指定してアイテム抽出が実行できるようにする予定です。またコンストレインツ設定がない高速信号ネットの抽出など、特定の属性が抜けていることを条件にしたアイテム抽出にも対応する予定です。

【Design Gateway 2020】について

Design Gateway 2018.0より進めてきたコンストレインツブラウザ統合の最終段階として、Design Force と Design Gateway 間でのバックアノテーション機能を完全なものとし、コンストレインツの完全整合を実現します。

DRC機能もさらに拡張し、任意属性で細分化したネットの種類ごとにルールチェックが行えるようにする予定です。

サーキットアドバイザでは、IC に接続するダンピング抵抗などの範囲チェック、端子入力電圧の範囲を電位差や割合で指定する機能などを追加する予定です。

ネット電圧値計算の機能拡充として、IC /コネクタピンへのモデルやパラメータが設定できるよう対応し、SPICEモデルの入手が困難なデバイスに対して、各ピンにモデルを割り付けることで、より高い精度のSPICE解析が行えるようになります。

その他、大規模化する回路規模や多ピン化に対応するためにキャンバス描画のパフォーマンスの向上やシートのアウトラインペインへの対応など、CADとしての基本機能の強化を予定しています。

DRC機能もさらに拡張し、任意属性で細分化したネットの種類ごとにルールチェックが行えるようにする予定です。

サーキットアドバイザでは、IC に接続するダンピング抵抗などの範囲チェック、端子入力電圧の範囲を電位差や割合で指定する機能などを追加する予定です。

ネット電圧値計算の機能拡充として、IC /コネクタピンへのモデルやパラメータが設定できるよう対応し、SPICEモデルの入手が困難なデバイスに対して、各ピンにモデルを割り付けることで、より高い精度のSPICE解析が行えるようになります。

その他、大規模化する回路規模や多ピン化に対応するためにキャンバス描画のパフォーマンスの向上やシートのアウトラインペインへの対応など、CADとしての基本機能の強化を予定しています。

【Circuit DR Navi 2020】 について

Circuit DR Navi 2020以降では、ガイドライン機能のブラッシュアップや自動チェック系ツールからのインポートなどを予定しています。チェックのための準備など定型的な作業を Circuit DR Navi を介して行えるようにしたり、サーキットアドバイザの結果を参照するなど、デザインレビューのプラットフォームとしての機能を拡張します。