会期後レポート

【ZIW2018】CR-8000 Design Force ロードマップ Part.3半導体/パッケージ/基板協調設計

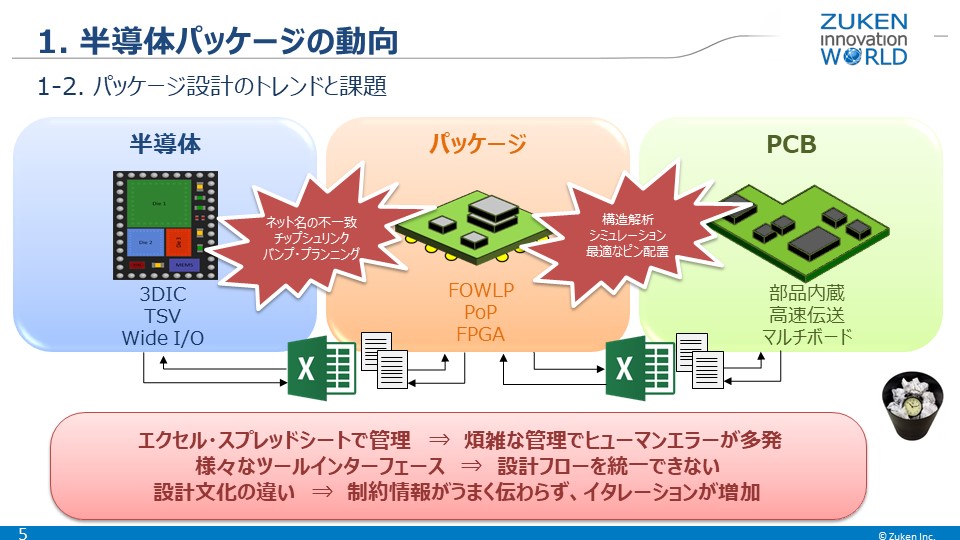

2018年12月18日パッケージ設計のトレンドと課題

従来、半導体/パッケージ/基板の設計は、それぞれ閉じた環境で最適化が行われてきましたが、協調設計のニーズが高まるにつれ、データ連携が大きな課題となっています。異なる設計環境間では、エクセルなどを用いた情報の受け渡しになりデータの標準化ができておらず、人手による煩雑な管理でヒューマンエラーの多発や設計環境文化の違いによるイタレーションの増加などの問題が発生しています。

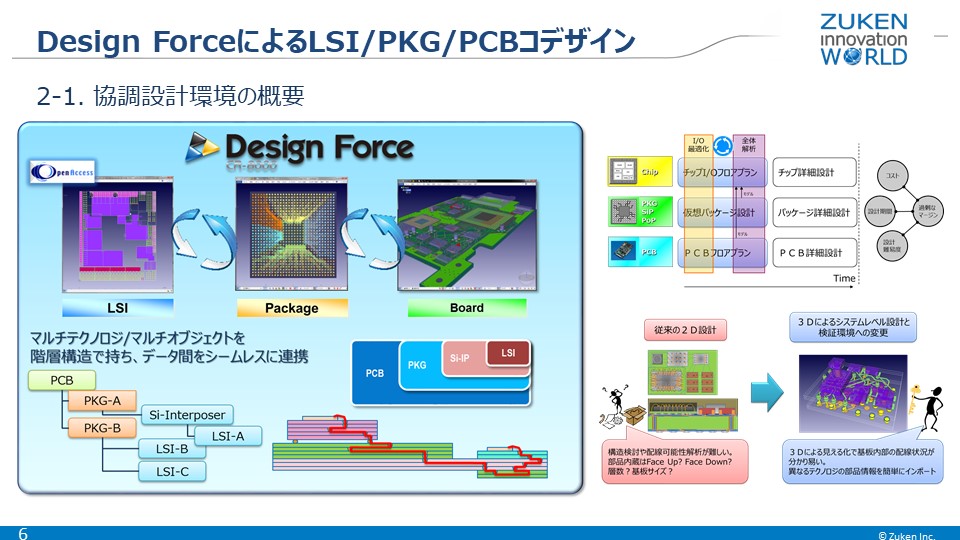

Design Force の協調設計環境

図研では、このような課題にいち早く取り組み、オープンアクセスという半導体専用のデータベースを使用し、Synopsys社、Mentor Graphics社、Cadence社などの半導体EDAツールとのシームレスな連携を実現し、さらに図研独自のレイアウトデータベースを組み合わることにより、半導体/パッケージ/基板のデータを階層的に持ち、1つのツール内ですべてのデータの表示や編集ができる環境を実現しました。

このユニークなコ・デザイン環境に、独自の自動配線機能や三次元技術を加えることで、構想設計から詳細設計まで扱うことができようなクイックプロトタイピングや三次元SiPのような設計を強力に支援できる環境を提供しています。

このユニークなコ・デザイン環境に、独自の自動配線機能や三次元技術を加えることで、構想設計から詳細設計まで扱うことができようなクイックプロトタイピングや三次元SiPのような設計を強力に支援できる環境を提供しています。

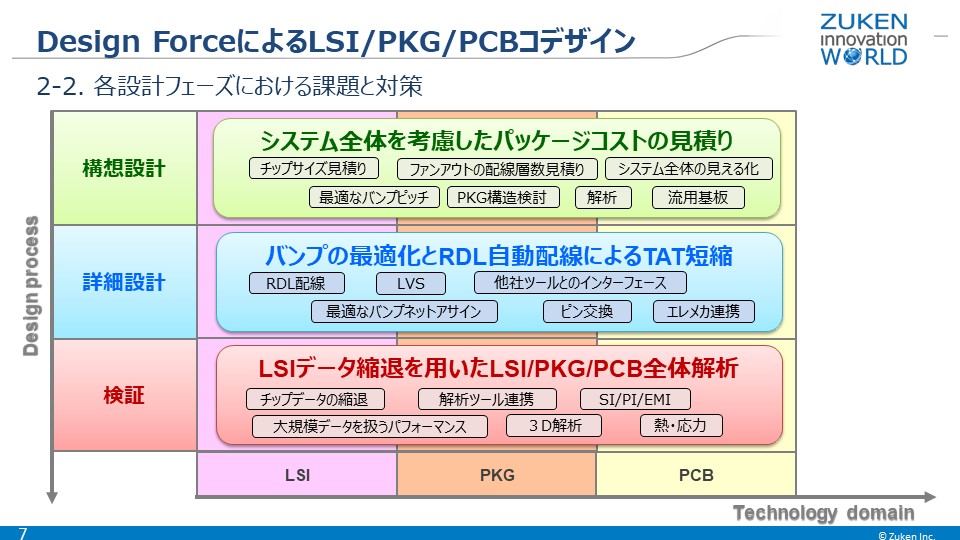

この Design Force の協調設計環境は、様々な設計フェーズで活用いただいており、構想設計段階におけるシステム全体を考慮したパッケージコストの見積もりや詳細設計段階におけるI/Oの最適化やイタレーションの削減、検証段階でのシステム全体の解析など、お客様の協調設計の課題を広範囲にカバーしています。

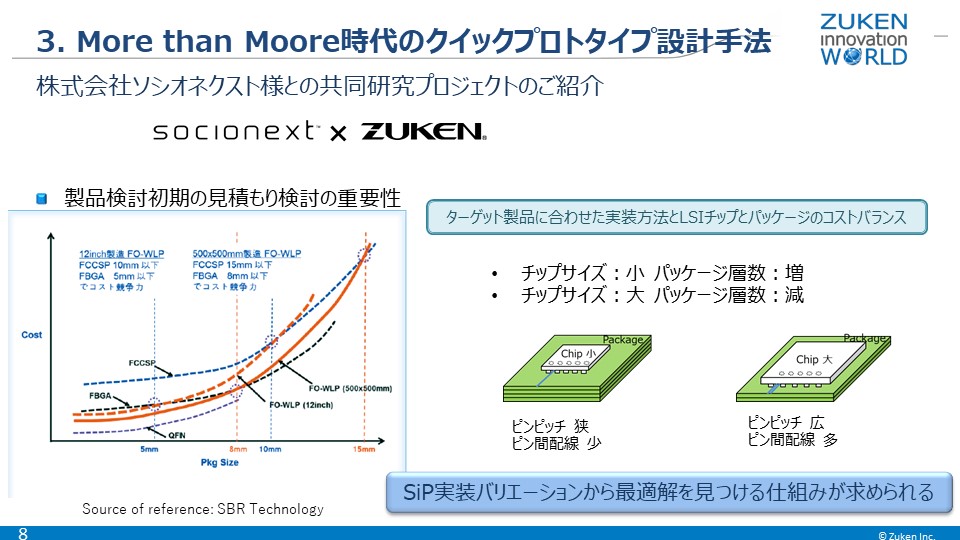

構想設計段階の活用事例 ― ソシオネクスト様との共同研究ブロジェクト

構想設計での Design Force 協調設計の活用事例として、株式会社ソシオネクスト様と図研との共同研究プロジェクトの一部をご紹介します。

年々、先端パッケージのコストが増大し、製品検討初期の見積もり検討におけるチップサイズとパッケージ層数のトレードオフ検討がコスト削減の重要な課題になっており、この課題検討がこのプロジェクトのきっかけでした。

見積もり検討では、FCCSP や FOWLP、FBGA など多種から、パッケージサイズに応じて最適なタイプを選定し、それに応じてチップサイズやパッケージ層数などの最適なパラメータを見つける仕組みが求められています。

年々、先端パッケージのコストが増大し、製品検討初期の見積もり検討におけるチップサイズとパッケージ層数のトレードオフ検討がコスト削減の重要な課題になっており、この課題検討がこのプロジェクトのきっかけでした。

見積もり検討では、FCCSP や FOWLP、FBGA など多種から、パッケージサイズに応じて最適なタイプを選定し、それに応じてチップサイズやパッケージ層数などの最適なパラメータを見つける仕組みが求められています。

LSI側もプロセスノードの微細化によりコストが増大し、先端テクノロジーを用いることができない多品種少量生産においては、特にコスト検討が重要になっています。

そこでチップを分割し、性能が必要な機能ブロックは先端テクノロジーを用い、それ以外の機能ブロックは従来のテクノロジー法で設計するような、チップ分割による製品の要求性能達成とコスト削減の両立の検討も行われました。

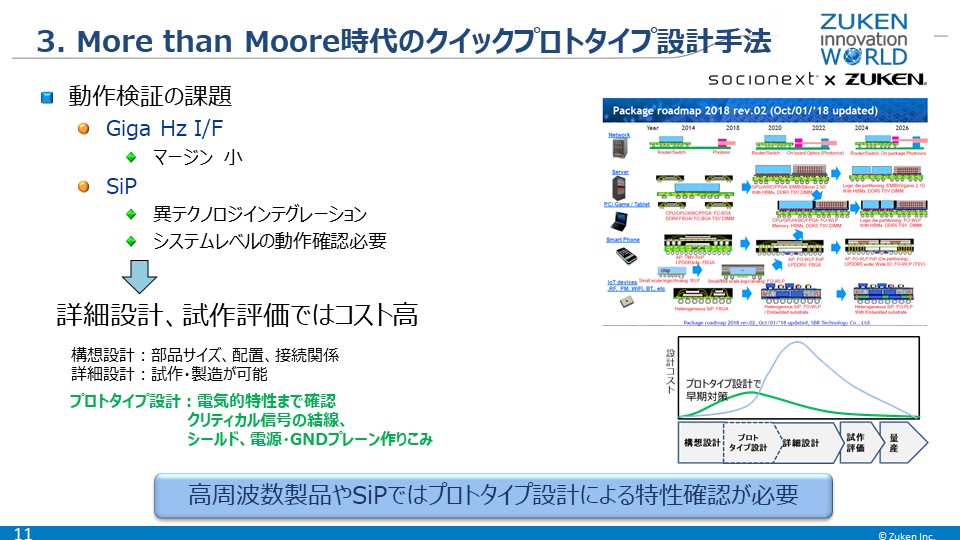

さらに、チップやパッケージの選択だけでなく、本当に期待する性能が得られるか、SiP設計では異なるテクノロジーの統合のため、システムレベルの動作確認も必要になります。

これらの検証を詳細設計段階で行うとコスト高になり、構想設計段階では行うには、情報不足により検証ができません。そこで、ソシオネクスト様では、構想設計の後に電気的な特性が確認できるレベルまで設計を追い込む、プロトタイプ設計 を取り入れ、そこで Design Force を活用されています。

そこでチップを分割し、性能が必要な機能ブロックは先端テクノロジーを用い、それ以外の機能ブロックは従来のテクノロジー法で設計するような、チップ分割による製品の要求性能達成とコスト削減の両立の検討も行われました。

さらに、チップやパッケージの選択だけでなく、本当に期待する性能が得られるか、SiP設計では異なるテクノロジーの統合のため、システムレベルの動作確認も必要になります。

これらの検証を詳細設計段階で行うとコスト高になり、構想設計段階では行うには、情報不足により検証ができません。そこで、ソシオネクスト様では、構想設計の後に電気的な特性が確認できるレベルまで設計を追い込む、プロトタイプ設計 を取り入れ、そこで Design Force を活用されています。

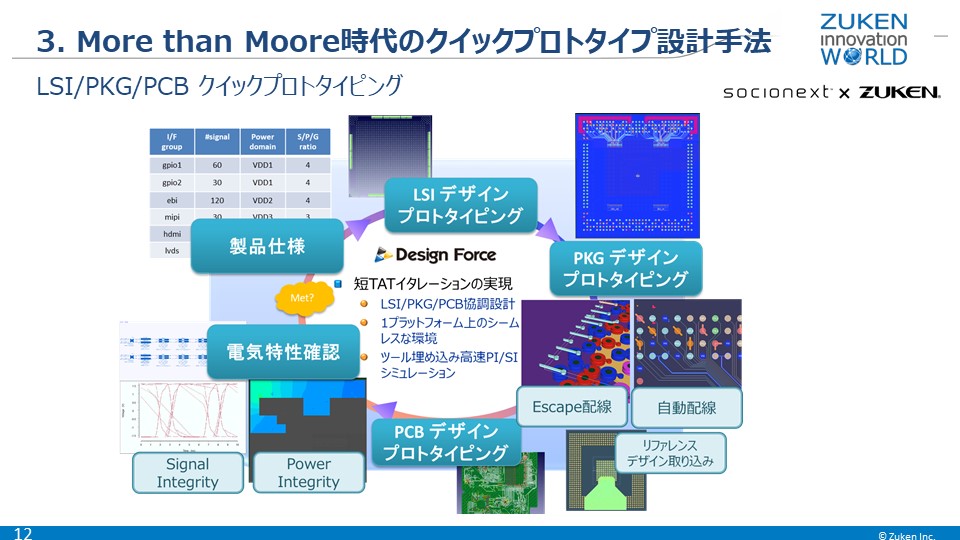

インプットとなる製品仕様は、エクセルなどのドキュメントを用い、まずLSIのプロトタイピングから開始します。次に、LSIやパッケージのデータを作成し、リファレンスデザインや流用設計などを用いながら自動配線を行い、PCB設計のプロトタイピングを行います。さらに Design Force の中でSIやPIなどの電気的特性を確認するところまでを行い、この短いサイクルを繰り返すことで製品仕様を固めていきます。

このプロジェクトでは、実際にこの手法を用いて FCCSP と FOWLP で比較し、電気特性解析としてクロストーク解析や電圧ノイズ解析、SI/PI解析を行っています。その結果とコストと照合することで、電気的特性を見極めながらコストとのトレードオフ検討を行うことができました。

今後は、他のLSIやパッケージの組み合わせを検討しながら、さらに短期間でのプロトタイプ設計ができる環境をソシオネクスト様と構築していく予定です。

今後は、他のLSIやパッケージの組み合わせを検討しながら、さらに短期間でのプロトタイプ設計ができる環境をソシオネクスト様と構築していく予定です。

協調設計活用事例 ― フリップチップパッケージ設計

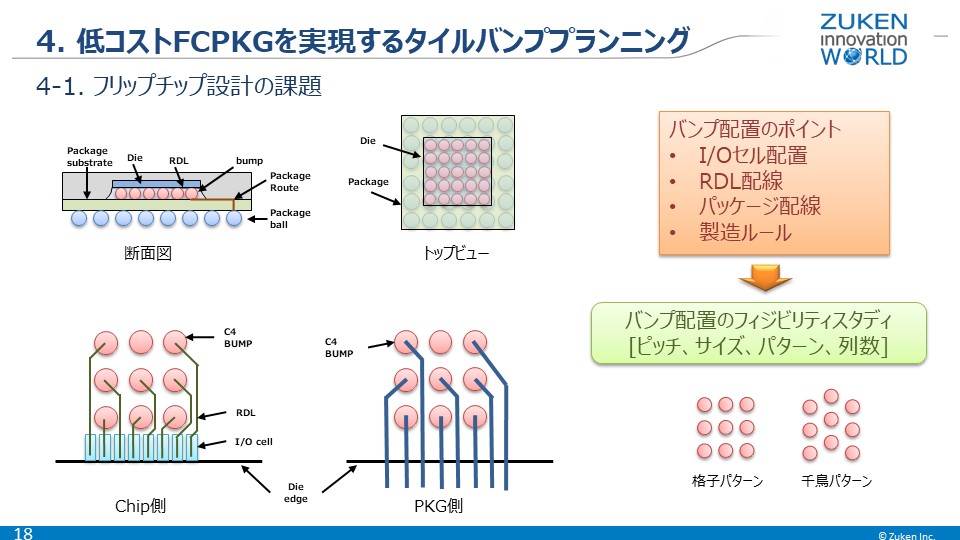

フリップチップパッケージ設計(FCPKG設計)では、シリコンバンプでチップとパッケージ間を接続します。

チップ側はI/Oセルを配置してバンプとRDL配線をし、パッケージ側は同じバンプに対してファンアウト配線します。ここで、限られた面積に収まるようにバンプのピッチやサイズ、パターン、ネットアサインなどを検討し、チップ側とパッケージ側の両方のデザインを見て最適化しなければなりません。

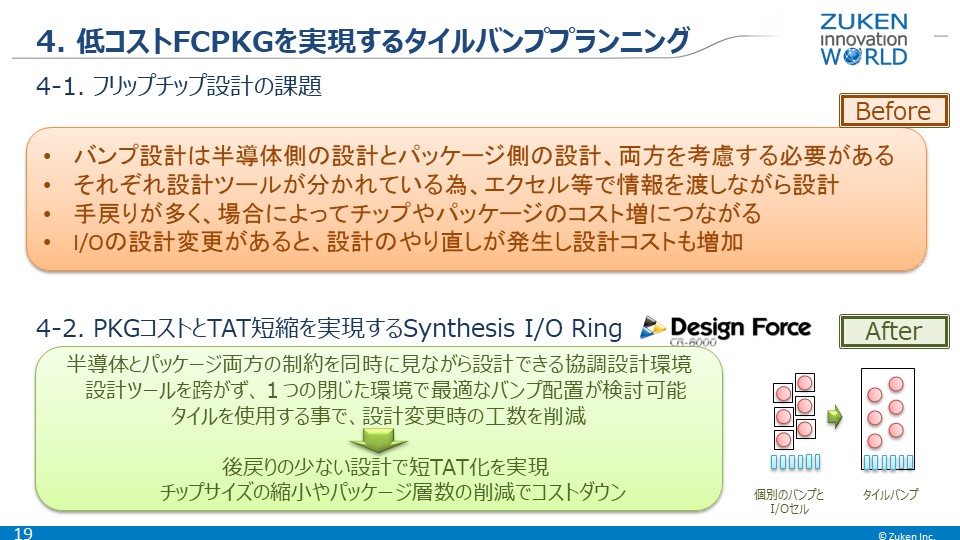

このようにバンプ設計は、半導体側とパッケージ側の両方を考慮する必要があり、半導体側とパッケージ側のツールが異なると、その間の情報のやり取りをエクセルなどで管理しなくてはならず、手戻りが多く発生したり、I/Oの設計変更に対してやり直しが発生するなど、コスト面や納期における大きな課題となっていました。

チップ側はI/Oセルを配置してバンプとRDL配線をし、パッケージ側は同じバンプに対してファンアウト配線します。ここで、限られた面積に収まるようにバンプのピッチやサイズ、パターン、ネットアサインなどを検討し、チップ側とパッケージ側の両方のデザインを見て最適化しなければなりません。

このようにバンプ設計は、半導体側とパッケージ側の両方を考慮する必要があり、半導体側とパッケージ側のツールが異なると、その間の情報のやり取りをエクセルなどで管理しなくてはならず、手戻りが多く発生したり、I/Oの設計変更に対してやり直しが発生するなど、コスト面や納期における大きな課題となっていました。

Design Force では、半導体とパッケージの両方のデータを1つのツールで持ち、両方の制約を考慮しながら協調設計できる環境になっています。また、バンプを個々に取り扱うのではなく、バンプの固まり(タイルバンプ)をバンプテンプレートとし、このテンプレートを用いてバンプ配置を行い、さらにパッケージ側の自動配線や配線性の確認も行うことができます。このバンプテンプレートに半導体とパッケージの両方の制約を入れることで、短時間で最適なI/Oプランニングが可能となり、設計変更に対しても柔軟に対応する事ができるようになります。

現在、こういった用途での Deisign Force の活用も増えてきています。

現在、こういった用途での Deisign Force の活用も増えてきています。

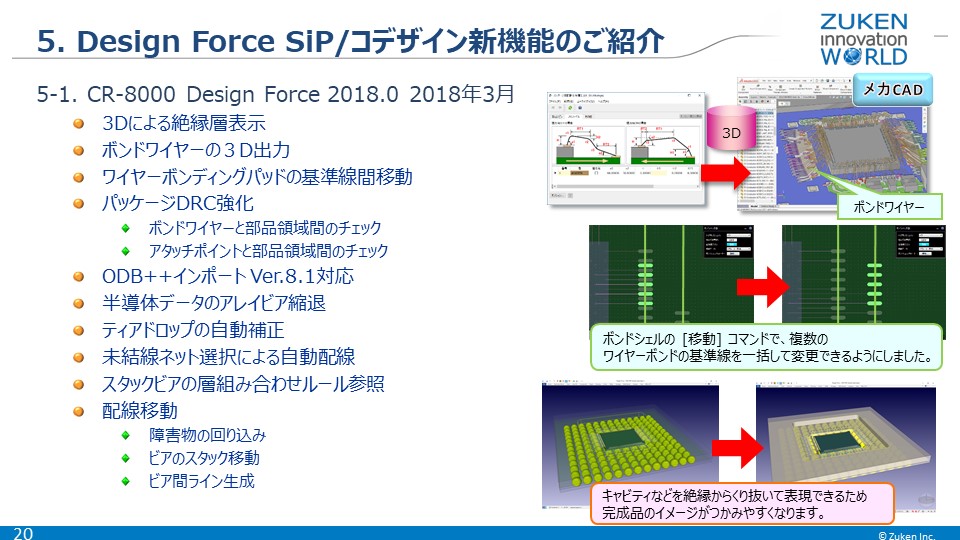

【Design Force 2018.0】SiP/コデザイン新機能

2018年3月のリリースでは、絶縁層の3D表示を実現しました。イメージセンサのパッケージでは、キャビティなどをパッケージに掘り、そこにチップを埋め込んで実装する場合がありますが、絶縁層を含めて三次元で表示することでより完成品に近いイメージが得られます。

また、ボンディングワイヤーの三次元の情報をメカCADに出力したり、複数のワイヤーボンドの基準線を一括変更できる機能を追加しています。

また、ボンディングワイヤーの三次元の情報をメカCADに出力したり、複数のワイヤーボンドの基準線を一括変更できる機能を追加しています。

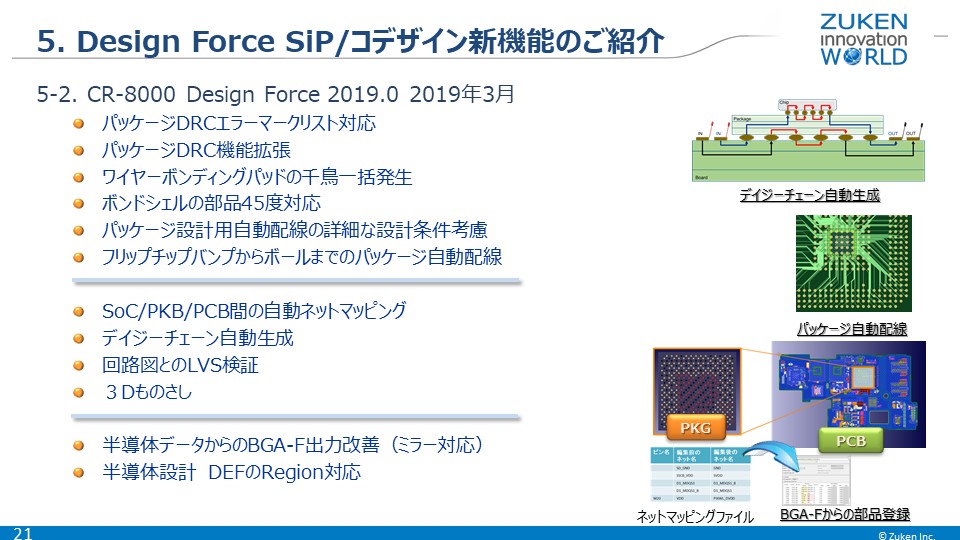

【Design Force 2019.0】SiP/コデザイン新機能

2019年3月のリリースでは、パッケージDRCの機能強化やパッケージの自動配線の際に、より詳細な条件を考慮できるような改善が含まれる予定です。また、フリップチップパッケージのボールまで自動で配線できる新しいツールもリリースする予定です。

さらに、半導体/パッケージ/基板間の自動ネットマッピング機能、多ピン化が進み自動化のニーズが高まるTEGチップ設計におけるデイジーチェーン自動生成機能も追加する予定です。

さらに、半導体/パッケージ/基板間の自動ネットマッピング機能、多ピン化が進み自動化のニーズが高まるTEGチップ設計におけるデイジーチェーン自動生成機能も追加する予定です。

【Design Force 2020.0】SiP/コデザイン新機能

2020年3月のリリースでは、フリップチップだけでなく、ワイヤーボンドとパッケージ間の自動配線も追加する予定です。またIEEE 2401に提案しているJEITA LPB V3.1への対応も計画しています。

今後の活動計画

・大学連携

現在、UCLAの「CHIPS」プロジェクトやジョージア工科大学におけるガラスインターポーザーのモックアップ作りに Design Force が活用されています。その他にも、台湾の国立交通大学やドイツのフラウンホーファー研究機構とも会話を始めており、今後このような大学や研究機関との共同開発にも積極的に取り組む予定です。

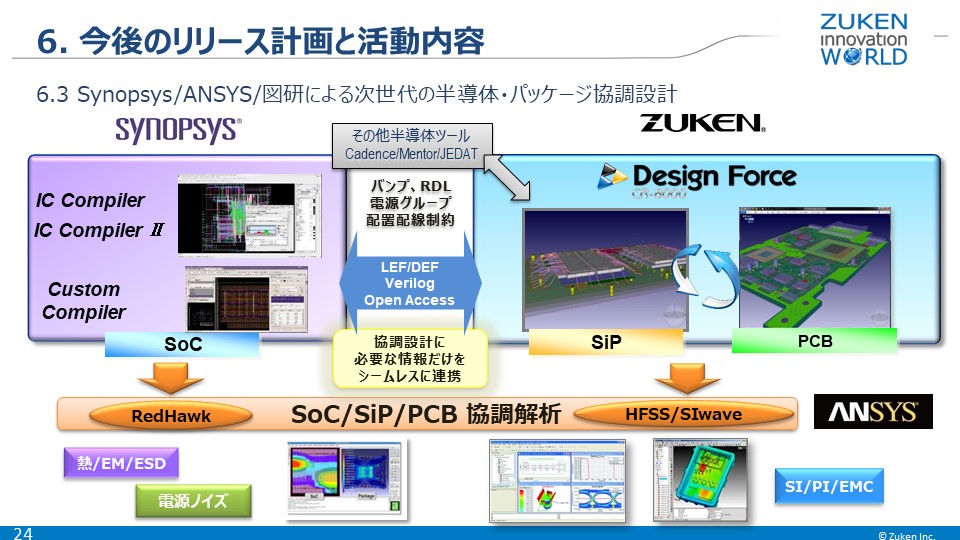

・Synopsys社、ANSYS社との連携

Synopsys社、ANSYS社との連携により、次世代の半導体・パッケージ協調設計環境の提供を目指します。3D-ICを含む、マルチチップに対応したIC CompilerⅡ(Synopsys社)と Design Force のコ・デザイン環境を融合し、ANSYS社の協調解析環境をインテグレートすることで、ヘテロジニアスなデバイスを支援する新たな協調設計環境を構築します。

このような新しいソリューションにも是非ご期待ください。

このような新しいソリューションにも是非ご期待ください。

|

|