☑Products

図研ベテランSEによる知って得する機能解説

-GPM編-

2011.03.24

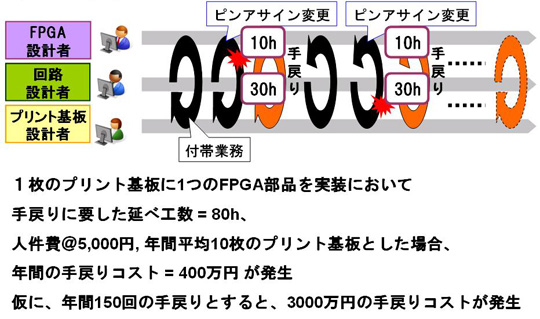

■手戻りコストはどのくらいか

では、こうした手戻りを費用換算すると、どのくらいになるのでしょう。実例をひとつ、少々楽観ベースで紹介しますので、皆さんのご経験に照らし合わせてご一考いただければと思います。

1枚のプリント基板にFPGAを1個実装する設計において、手戻り二回のピンアサイン変更が発生したとします。

一回目のピン変更リストをもとに、FPGA設計側でコンストレインツ反映およびインプリメントに10時間、回路図およびプリント基板への情報反映に30時間かかったとします。二回目も同程度の時間がかかったとします。合計で80時間。約10人日相当になるでしょうか。仮に人件費を5千円/hに設定した場合、40万円の費用が生じたことになります。

年間10枚のプリント基板を起こし、毎回同じ程度の手戻りによるピンアサイン変更が生じた場合、年間400万円のコスト増しとなります。

プリント基板に複数個のFPGAを実装するとなると、その数分だけコストが増大していきます。

実例ベースですが、近似値としており数値及び費用は実際のものではありません。

流用性が無い、少量多品種の製品を開発する場合はどうでしょう。上記の例に、年間延べ150回のピンアサイン変更が生じたとすると、年間3千万円のコストが発生することになります。

皆様の場合は、いかがでしょうか?

■もし、こんなことができたら。。。

【もし、ピンアサイン変更の情報を手軽に反映できるツールがあったら。。。】

このようなツールがあったら、先程の手戻りコストを大幅に削減できると思いませんか?

あるのです!それが、『GPM』です。

![]()

そして、現場の設計者の方々は、「もしこんなことができたら付帯業務を減らせるしミスも減るのだけれどなぁ~」と、思っていることがあるのではないでしょうか?それは、概ね共通しているかと思います。

ここでは、「もし、こんなことができたら」という形式で、GPMで出来ることをご紹介したいと思います。

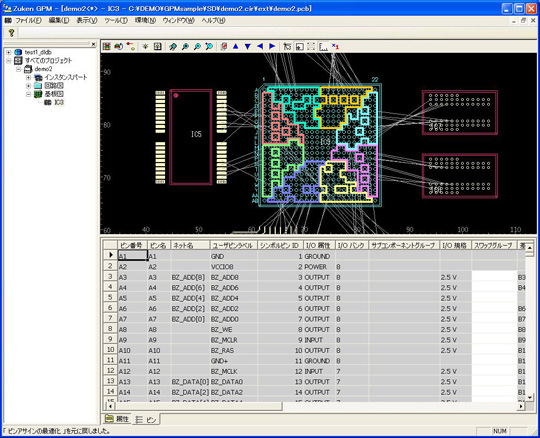

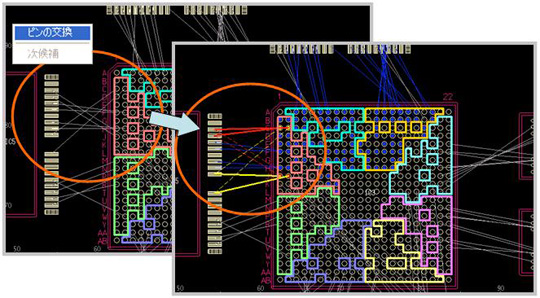

【もし、プリント基板図を開いて簡単な操作でピンアサインを検討ができたら。。。】

FPGA設計者もしくは兼務する回路設計者は、

『今までプリント基板設計者に配線パターン交差の有無を確認してもらっていて待ち時間を要していたけど、自分で確認できるのに・・・』

プリント基板設計者は、

『パターン交差を無くするピンアサイン変更をFPGA設計者に要求や提案ができるのに・・・』

という、各々の思いが生まれてくると思います。

できるのです!

GPMは、誰でも回路図とプリント基板図を開くことができ、ラッツネストを掴んでピンアサイン検討することができる環境を提供しています。

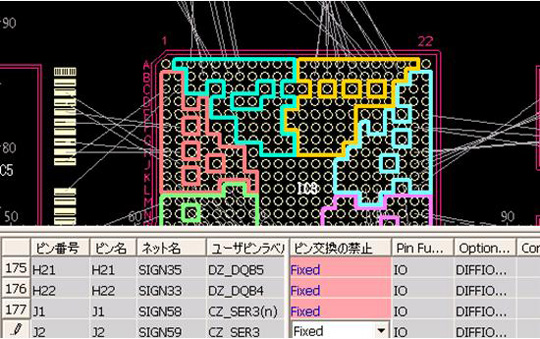

ただ、どのピンとでもアサイン変更ができるというものではありません。対象デバイスの電源・グランド・NC・予約ピンの考慮に加えて、クロックピン・I/Oバンク毎のサポートI/O規格・入出力の制約も考慮して、ピンアサイン変更を制限しています。

LVDS等の差動ペアの自動判定も行っていますので、差動信号の場合、ポジ/ネガのペアでピンアサイン変更が可能になっています。

ピンアサイン変更の検討が済んで、後で誤って交換しないように、任意にロックをかけることもできます。

前のページへ

前のページへ