☑アナログ&ミックスド・シグナル回路の設計と

基板レイアウトで知っておくべき基礎技術

12. デジタル回路の部分もなめてかかってはいけない①

アナログ・デバイセズ株式会社 石井 聡

2011.07.21

12-3 コンバータICでデジタルI/Fでミックスド・シグナルのノイズについて考えるべきこと

プロセッサやDSPに比べて、ほとんどのコンバータICの出力段は、高電流出力型ではなく、ファンアウトが小さくなっています。

プリント基板上のアナログ・グラウンドに、コンバータIC出力のデジタル信号のリターン電流が流れます(理由は連載の第7回で述べたとおり)。プリント基板上のアナログ回路部分で、デジタル信号により生じるノイズを最小限に抑えるには、このリターン電流をできるだけ低く抑える必要があります。

■CMOS ICを使うことが実際だが、スイッチング時の過渡電流は結構大きい

負荷となる素子として、TTL ICではなくCMOS ICを使用することがポイントです。現代の回路設計では、CMOS ICを使うことが当然かつ現実的でしょう。

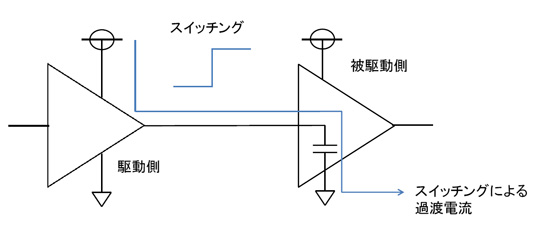

CMOS ICのDC入力電流はほぼゼロです。しかし入力容量はそれほど低くないため、スイッチング時の過渡電流は結構大きくなります。図12-3のように、この大きい過渡電流がアナログ・グラウンドの経路に流れ、ノイズを生じることもありますので、とくにI/Fのバス転送レートが高速になる場合は、十分に注意すべきところでしょう。

図12-3 スイッチング時の過渡電流がアナログ・グラウンドに流れノイズを生じる

■バスを直接駆動させずバッファICでバッファリングする

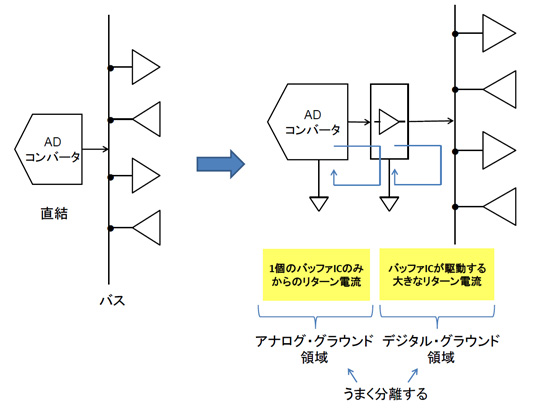

コンバータIC出力のデジタル電流を最小限に抑えるには、図12-4に示すように、複数のCMOS ICが接続されている「バス」を、コンバータIC出力で直接駆動させずに、バッファICを用いて一旦バッファリングするとよいでしょう。

こうするとコンバータICが駆動するのは1個のバッファICだけとなり、このリターン電流のみがアナログ・グラウンド経路に流れることになります。バッファICから、複数のCMOS IC負荷(バスなど)のリターン電流が流れるデジタル・グラウンドを、アナログ・グラウンドとうまく分離すれば、リターン電流がこのデジタル・グラウンド部分のみを流れることになります。これによりコンバータICに対してのデジタル・ノイズの影響を低減させることもできます。

またこのようなバッファICを用いると、プリント基板上のデジタル回路部分のデジタル・ノイズからコンバータICを分離することもできます(バッファICがノイズを堰き止めてくれるため)。

図12-4 バスを直接駆動させずバッファICでバッファリングする

■抵抗を直列に挿入して過渡的に流れる電流を軽減させる

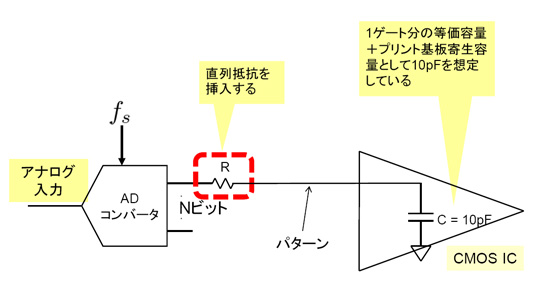

タイミング・マージンが間に合えば、図12-5のように抵抗を直列に挿入して、CMOS ICの入力容量とでローパスフィルタを形成させ、過渡的に大きく流れるスイッチング電流を軽減させることができます。

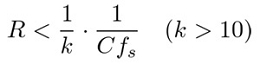

この抵抗Rの大きさは、CMOS ICの入力容量をC[F]、コンバータICのシステム・クロック(バス転送レート)をfs[Hz]とすると、

で概略を求めることができます。ここでkは時定数に対する係数で、kは10より大きい値にしておくと良いでしょう。

あまりに時定数が長すぎて、信号の変化速度が遅くなると、負荷となるCMOS IC内部を電源からグラウンドに流れる「貫通電流」が大きくなってしまうので、適度な時定数に抑えることが肝要です。

またこの対策の効用として、パターンのインダクタンスと入力容量とで生じる「リンギング」と呼ばれる信号の暴れも軽減することができ、一石二鳥です。

図12-5 抵抗を直列に挿入して過渡的に流れる電流を軽減させる

12-4 まとめ

今回はミックスド・シグナル・システムのデジタル回路部分について考えてきました。「ミックスド・シグナル」という視点では、デジタル回路も十分に吟味しないと、目的の特性を出すことが難しいことがご理解いただけたかと思います。

次回は再度デジタル回路として、今度はアナログ的な要素も考慮すべき、タイミングやクロックの話題を示していきたいと思います。

●執筆者プロフィール

石井 聡

1985年第1級無線技術士合格。1986年東京農工大学工学部電気工学科卒業、同年双葉電子工業株式会社入社。

1994年技術士(電気・電子部門)合格。2002年横浜国立大学大学院博士課程後期(電子情報工学専攻・社会人特別選抜)修了。博士(工学)

2009年アナログ・デバイセズ株式会社入社、現在コアマーケット統括部マネージャ。新規ビジネス創生、セミナ・トレーニング、技術サポートなど多岐な業務に従事。

前のページへ

前のページへ